HYDRA

Service Manual

2A-34

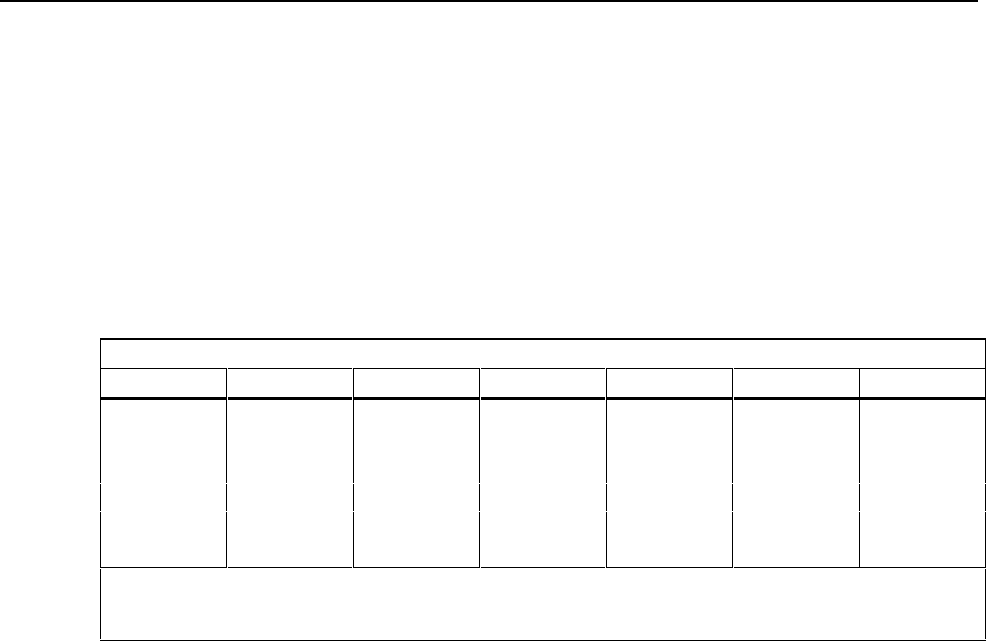

2A-65. Front Panel Switches

The FPGA scans the 19 Front Panel Switches (A2S1 through A2S18, and A2S21) using

only six interface signals (plus the ground connection already available from the power

supply). These six signals (SWR1 through SWR6) are connected to bidirectional I/O

pins on the FPGA. Each successive column has one less switch.

This arrangement allows the unused interface signals to function as strobe signals when

their respective column is driven by the FPGA. The FPGA cycles through six steps to

scan the complete Front Panel Switch matrix. Table 2A-7 shows the interface signal state

and, if the signal state is an output, the switches that may be detected as closed.

Table 2A-7. Front Panel Switch Scanning (2635A)

Interface Signal States or Key Sensed

Step SWR6 SWR5 SWR4 SWR3 SWR2 SWR1

1 A2S8 A2S17 A2S10 A2S12 A2S18 A2S13

2 A2S1 A2S2 A2S3 A2S4 A2S11 0

3 A2S7 A2S9 A2S5 A2S6 0 Z

4 A2S14 A2S15 A2S16 0 Z Z

5NANA0 Z Z Z

6 A2S21 0 Z Z Z Z

A2Sn indicates switch closure sensed.

0 indicated strobe driven to logic 0

Z indicated high impedance input; state ignored.

In step 1, six I/O pins are set to input, and the interface signal values are read. In steps 2

through 6, the pin listed as O is set to output zero, the other pins are read, and pins

indicated by a Z are ignored.

Each of the interface signals is pulled up to the +5V dc supply by a 10-kΩ resistor in

network A2Z1. Normally, the resistance between any two of the interface signals is

approximately 20 kΩ. Checking resistances between any two signals (SWR1 through

SWR6) verifies proper termination by resistor network A2Z1.

2A-66. Display

The custom vacuum-fluorescent display (A2DS1) comprises a filament, 11 grids

(numbered 0 through 10 from right to left on the display), and up to 14 anodes under

each grid. The anodes make up the digits and annunciators for their respective area of the

display. The grids are positioned between the filament and the anodes.

A 5.4V ac signal, biased at a -24V dc level, drives the filament. When a grid is driven to

+5V dc, the electrons from the filament are accelerated toward the anodes that are under

that grid. Anodes under that grid that are also driven to +5V dc are illuminated, but the

anodes that are driven to -30V dc are not. Grids are driven to +5V dc one at a time,

sequencing from GRID(10) to GRID(0) (left to right, as the display is viewed.)

2A-67. Beeper Drive Circuit

The Beeper Drive circuit drives the speaker (A2LS1) to provide an audible response to a

button press. A valid entry yields a short beep; an incorrect entry yields a longer beep.

The circuitry comprises a dual four-bit binary counter (A2U4) and a NAND gate (A2U6)

used as an inverter. One four-bit free-running counter (A2U4) divides the 1.024-MHz

clock signal (E) from the FPGA (DSCLK) by 2 to generate the 512-kHz clock (CLK1)

used by the Display Controller. This counter also divides the 1.024-MHz clock by 16,

generating the 64-kHz clock that drives the second four-bit binary counter (A2U4).