www.ti.com

4.8InterruptHandling

InterruptConditions

immediatelystartsdown-countingeachtimetheCPUwritestheseregisters.Whentheratecontrolcounter

registeriswritten,andthecountervaluereacheszero(notethattheCPUmaywritezeroimmediatelyfor

azerocount),theinterruptpulsegenerationlogicisallowedtofireasinglepulseifanybitsinthe

correspondingICSRregisterbitsareset(orbecomesetafterthezerocountisreached).Thecounter

remainsatzero.Whenthesinglepulseisgenerated,thelogicwillnotgenerateanotherpulse,regardless

ofinterruptstatuschanges,untiltheratecontrolcounterregisteriswrittenagain.

Aninterruptratecontrolregister(INTDSTn_RATE_CNTL)isimplementedforeachsupportedphysical

interruptdestination.Thedevicesupportsuptoeightinterruptdestinations,INTDST0–INTDST7.The

namesoftheregistersandtheiraddressoffsetsare:

•INTDST0_RATE_CNTL(Addressoffset0320h)

•INTDST1_RATE_CNTL(Addressoffset0324h)

•INTDST2_RATE_CNTL(Addressoffset0328h)

•INTDST3_RATE_CNTL(Addressoffset032Ch)

•INTDST4_RATE_CNTL(Addressoffset0330h)

•INTDST5_RATE_CNTL(Addressoffset0334h)

•INTDST6_RATE_CNTL(Addressoffset0338h)

•INTDST7_RATE_CNTL(Addressoffset033Ch)

Ifinterruptpacingisnotdesiredforaparticularinterruptdestination,theCPUmuststillwrite00000000h

intotheINTDSTn_RATE_CNTLregisterafterclearingthecorrespondingICSRbitstoacknowledgethe

physicalinterrupt.IfanICSRisnotmappedtoaninterruptdestination,pendinginterruptbitswithinthe

ICSRmaintaincurrentstatus.Whenenabled,theinterruptlogicre-evaluatesallpendinginterruptsand

re-pulsestheinterruptsignalifanyinterruptconditionsarepending.Thedown-counterisbasedonthe

DMAclockcycle.

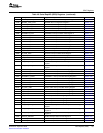

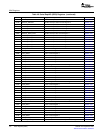

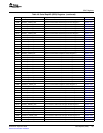

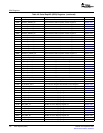

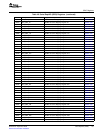

Figure62.INTDSTn_RATE_CNTLInterruptRateControlRegister

310

32-bitCountDownValue

R/W-0

LEGEND:R/W=Read/Write;-n=Valueafterreset

InterruptsareeithersignaledexternallythroughRapidIOpackets,orinternallybystatemachinesinthe

peripheral.CPUservicinginterruptsaresignaledexternallybytheDOORBELLRapidIOpacketindirect

I/Omode,orinternallybytheCPPImoduleinthemessagepassingmode.ErrorStatusinterruptsare

signaledwhenerrorcountinglogicwithintheperipheralhavereachedtheirthresholds.Ineithercase,itis

theperipheralthatsignalstheinterruptandsetsthecorrespondingstatusbits.

WhentheCPUisinterrupted,itreadstheICSRregisterstodeterminethesourceoftheinterruptand

appropriateactiontotake.Forexample,ifitisaDOORBELLinterrupt,theCPUwillreadfromanL2

addressthatisspecifiedbyitscircularbufferreadpointerthatismanagedbysoftware.Theremaybe

morethanonecircularbufferforeachcore.Thecorrectcircularbuffertoreadfromandincrement

dependsonthebitsetintheICSRregister.TheCPUthenclearsthestatusbit.

ForErrorStatusinterrupts,theperipheralmustindicatetoalltheCPUsthatoneofthelinkportshas

reachedtheerrorthreshold.Inthiscase,theperipheralsetsthestatusbitindicatingdegradedorfailed

limitshavebeenreached,andaninterruptisgeneratedtoeachcorethroughtheICRRmapping.The

corescanthenscantheICSRregisterstodeterminetheportwiththeerrorproblems.Furtheractioncan

thenbetakenasdeterminedbytheapplication.

100SerialRapidIO(SRIO)SPRUE13A–September2006

SubmitDocumentationFeedback