www.ti.com

4.6InterruptGeneration

4.7InterruptPacing

InterruptConditions

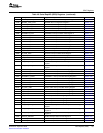

Figure61.ExampleDiagramofInterruptStatusDecodeRegisterMapping

Thefollowingaresuggestionsforminimizingthenumberofregisterreadstoidentifyingtheinterrupt

source:

•DedicateeachdoorbellICSRtoonecore.TheCPUcanthendeterminetheinterruptsourcefroma

singlereadofthedecoderegister.

•AssigntheRXandTXCPPIqueuesorthogonallytodifferentcores.TheCPUcanthendeterminethe

interruptsourcefromasinglereadofthedecoderegisters.Theonlyexceptionstothisarebits31and

30,whicharealsologicallyORedwithLSUandportinterruptsources.

Interruptsaretriggeredona0-to-1logic-signaltransition.Regardlessoftheinterruptsources,thephysical

interruptsaresetonlywhenthetotalnumberofsetICSRbitstransitionsfromnonetooneormore.The

peripheralisresponsibleforsettingthecorrectbitwithintheICSR.TheICRRregistermapsthepending

interruptrequesttotheappropriatephysicalinterruptline.ThecorrespondingCPUisinterruptedand

readstheISDRandICSRregisterstodeterminetheinterruptsourceandappropriateaction.Interrupt

generationisgovernedbytheinterruptpacingdiscussedSection4.7.

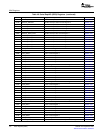

Therateatwhichaninterruptcanbegeneratediscontrollableforeachphysicalinterruptdestination.Rate

controlisimplementedwithaprogrammabledown-counter.Theloadvalueofthecounteriswrittenbythe

CPUintotheappropriateinterruptratecontrolregister(seeFigure62).Thecounterreloadsand

SPRUE13A–September2006SerialRapidIO(SRIO)99

SubmitDocumentationFeedback