www.ti.com

2.3.10ResetandPowerDown

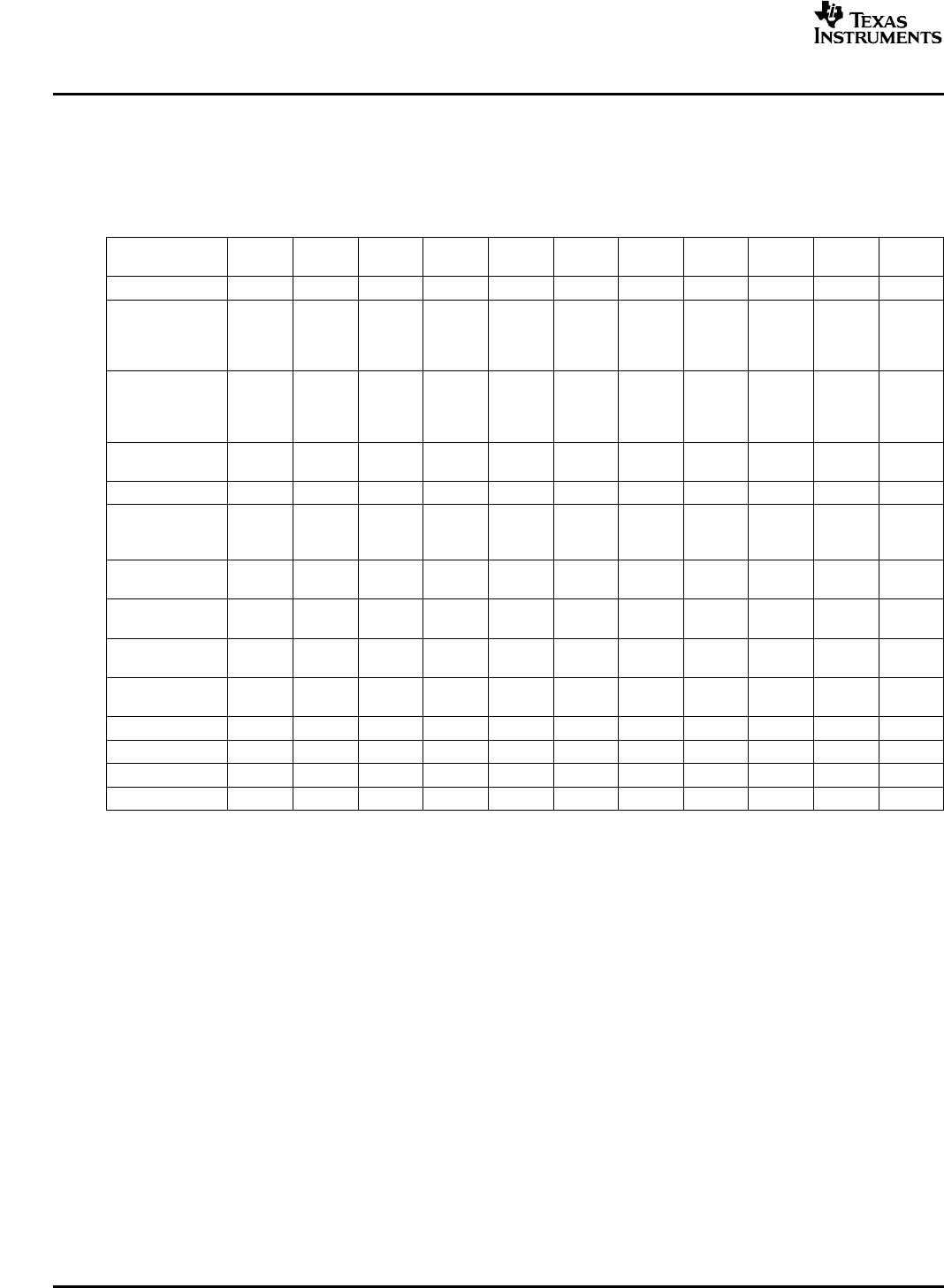

SRIOFunctionalDescription

TheRapidIOperipheralallowsindependentsoftwarecontrolledshutdownforthelogicalblockslistedin

Table26.WiththeexceptionofBLK0_ENforthememory-mappedregisters(MMRs),whentheBLKn_EN

signalsaredeasserted,theclocksaregatedtotheseblocks,effectivelyprovidingashutdownfunction.

Table26.ResetHierarchy

BusGBLBLK0BLK1BLK2BLK3BLK4BLK5BLK6BLK7BLK8

LogicalBlockReset_EN_EN_EN_EN_EN_EN_EN_EN_EN_EN

DMAinterface√√

MMRs:√√

Reset/power-

downcontrol

registers

MMRs:√√√

Non-reset/power-

downcontrol

registers

Interrupthandling√√

unit(IHU)

Trafficflowlogic√√

Congestion√√

controlunit

(CCU)

LSU(DirectI/O√√√

initiator)

MAU(DirectI/O√√√

target)

TXU(message√√√

passinginitiator)

RXU(message√√√

passingtarget)

Port0datapath√√√

Port1datapath√√√

Port2datapath√√√

Port3datapath√√√

ResetoftheSERDESmacrosishandledindependentlyoftheregistersdiscussedinthissection.The

SERDEScanbeconfiguredtoshutdownunusedlinksorfullyshutdown.SERDESTXandRXchannels

maybeenabled/disabledbywritingtobit0oftheSERDES_CFGTXn_CNTLand

SERDES_CFGRXn_CNTLregisters.ThePLLandremainingSERDESfunctionalblockscanbecontrolled

bywritingtotheENPLLsignalintheSERDES_CFG0_CNTLregister.ThisbitwilldrivetheSERDES

signalinput,whichwillgatethereferenceclocktotheseblocksinternally.Thisreferenceclockissourced

fromadevicepinspecificallyfortheSERDESandisnotderivedfromtheCPUclock,thusitresets

asynchronously.ENPLLwilldisableallSERDEShigh-speedoutputclocks.Sincetheseclocksare

distributedtoallthelinks,ENPLLshouldonlybeusedtocompletelyshutdowntheperipheral.Itshouldbe

notedthatshutdownofSERDESlinksinbetweennormalpackettransmissionsisnotpermissiblefortwo

reasons.First,theserialRapidIOsendsidlepacketsbetweendatapacketstomaintainsynchronization

andlanealignment.Withoutthismechanism,theRapidIORXlogiccanbemis-alignedforboth1Xand4X

ports.Second,thelocktimeoftheSERDESPLLwouldneedtoreoccur,whichwouldslowdownthe

operation.

WhentheSERDESENTXsignalisheldlow,thecorrespondingtransmitterispowereddown.Inthisstate,

bothoutputs,TXPandTXN,willbepulledhightoVDDT.

70SerialRapidIO(SRIO)SPRUE13A–September2006

SubmitDocumentationFeedback