www.ti.com

5.14SERDESTransmitChannelConfigurationRegistern(SERDES_CFGTXn_CNTL)

SRIORegisters

Therearefouroftheseregisters,tosupportfourports(seeTable59).ThegeneralformforaSERDES

transmitchannelconfigurationregisterissummarizedbyFigure75andTable60.SeeSection2.3.2.3for

acompleteexplanationoftheprogrammingfortheseregisters.

Table59.SERDES_CFGTXn_CNTLRegistersandtheAssociatedPorts

RegisterAddressOffsetAssociatedPort

SERDES_CFGTX0_CNTL0110hPort0

SERDES_CFGTX1_CNTL0114hPort1

SERDES_CFGTX2_CNTL0118hPort2(TMS320TCI6482Only)

SERDES_CFGTX3_CNTL011ChPort3(TMS320TCI6482Only)

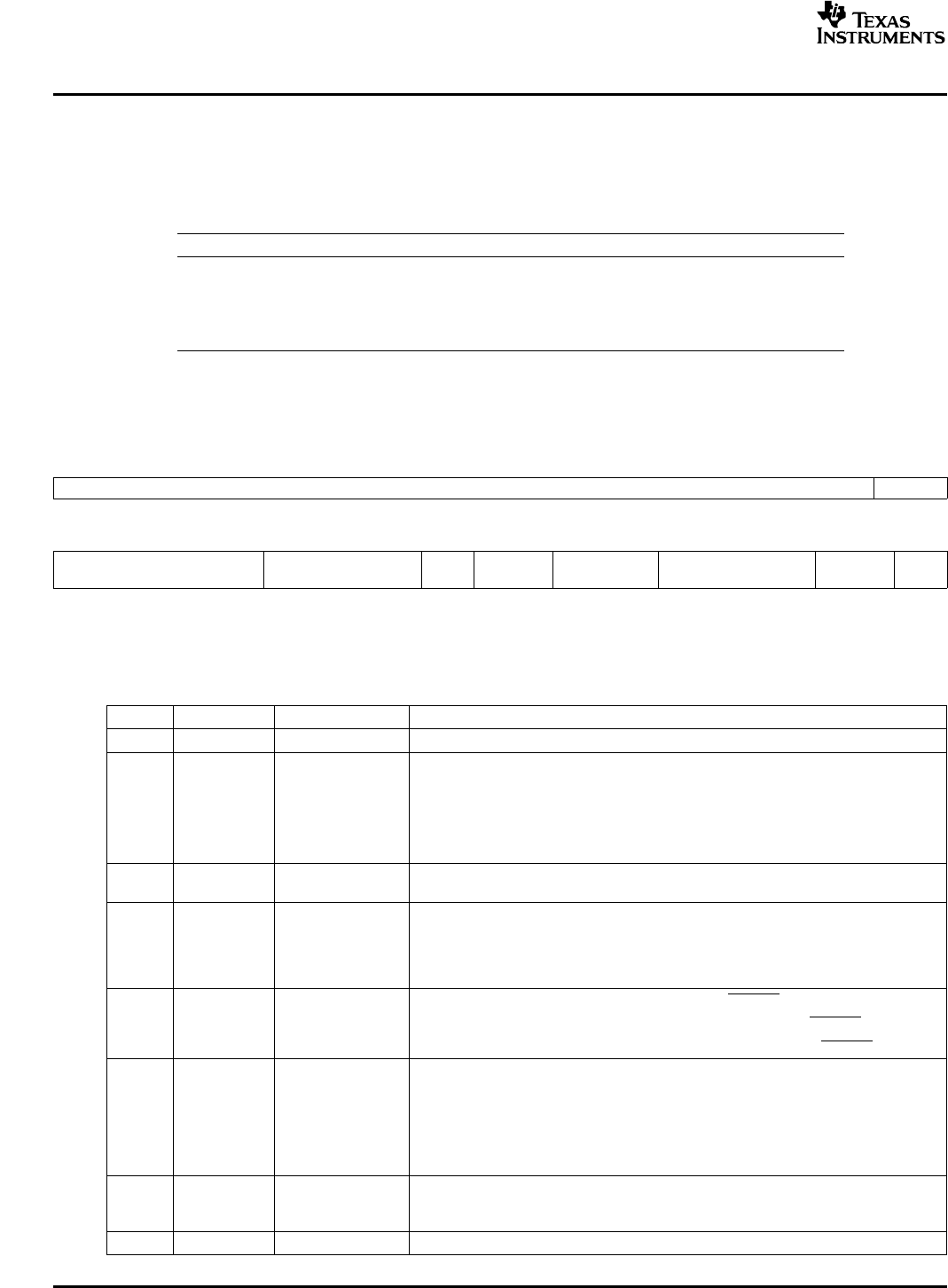

Figure75.SERDESTransmitChannelConfigurationRegistern(SERDES_CFGTXn_CNTL)

311716

ReservedENFTP

R-0R/W-0

151211987654210

—

DESWINGCMINVPAIRRATEBUSWIDTHENTX

(write0)

R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=Valueafterreset

Table60.SERDESTransmitChannelConfigurationRegistern(SERDES_CFGTXn_CNTL)Field

Descriptions

BitFieldValueDescription

31–17Reserved0Theseread-onlybitsreturn0swhenread.

16ENFTP1Enablesfixedphaserelationshipoftransmitinputclockwithrespecttotransmit

outputclock.Theonlyvalidvalueforthisfieldis1b;allothervaluesarereserved.

15–12DE0000b–1111bDe-emphasis.Selectsoneof15outputde-emphasissettingsfrom4.76to71.42%.

De-emphasisprovidesameanstocompensateforhighfrequencyattenuationin

theattachedmedia.Itcausestheoutputamplitudetobesmallerforbitswhichare

notprecededbyatransitionthanforbitswhichare.SeeTable61.

11–9SWING000b–111bOutputswing.Selectsoneof8outputamplitudesettingsbetween125and

1250mV

dfpp

.SeeTable62.

8CMCommonmode.Adjuststhecommonmodetosuittheterminationattheattached

receiver.

0Normalcommonmode.Commonmodenotadjusted.

1Raisedcommonmode.Commonmoderaisedby5%ofe

54

.

7INVPAIRInvertpolarity.InvertsthepolarityofRIOTXnandRIOTXn.

0Normalpolarity.RIOTXnisconsideredtobepositivedataandRIOTXnnegative.

1Invertedpolarity.RIOTXnisconsideredtobenegativedataandRIOTXnpositive.

6–5RATEOperatingrate.Selectsfull,half,orquarterrateoperation.

00bFullrate.TwodatasamplestakenperPLLoutputclockcycle.

01bHalfrate.OnedatasampletakenperPLLoutputclockcycle.

10bQuarterrate.OnedatasampletakeneverytwoPLLoutputclockcycles.

11bReserved

4–2BUSWIDTH000bBuswidth.Alwayswrite000btothisfield,toindicatea10-bit-wideparallelbusto

theclock.Allothervaluesarereserved.SeeSection2.3.2.1foranexplanationof

thebus.

1Reserved0Alwayswrite0tothisreservedbit.

128SerialRapidIO(SRIO)SPRUE13A–September2006

SubmitDocumentationFeedback