www.ti.com

5.13SERDESReceiveChannelConfigurationRegistern(SERDES_CFGRXn_CNTL)

SRIORegisters

Therearefouroftheseregisters,tosupportfourports(see).ThegeneralformforaSERDESreceive

channelconfigurationregisterissummarizedbyFigure74andTable57.SeeSection2.3.2.2fora

completeexplanationoftheprogrammingoftheseregisters.

Table56.SERDES_CFGRXn_CNTLRegistersandtheAssociatedPorts

RegisterAddressOffsetAssociatedPort

SERDES_CFGRX0_CNTL0100hPort0

SERDES_CFGRX1_CNTL0104hPort1

SERDES_CFGRX2_CNTL0108hPort2(TMS320TCI6482Only)

SERDES_CFGRX3_CNTL010ChPort3(TMS320TCI6482Only)

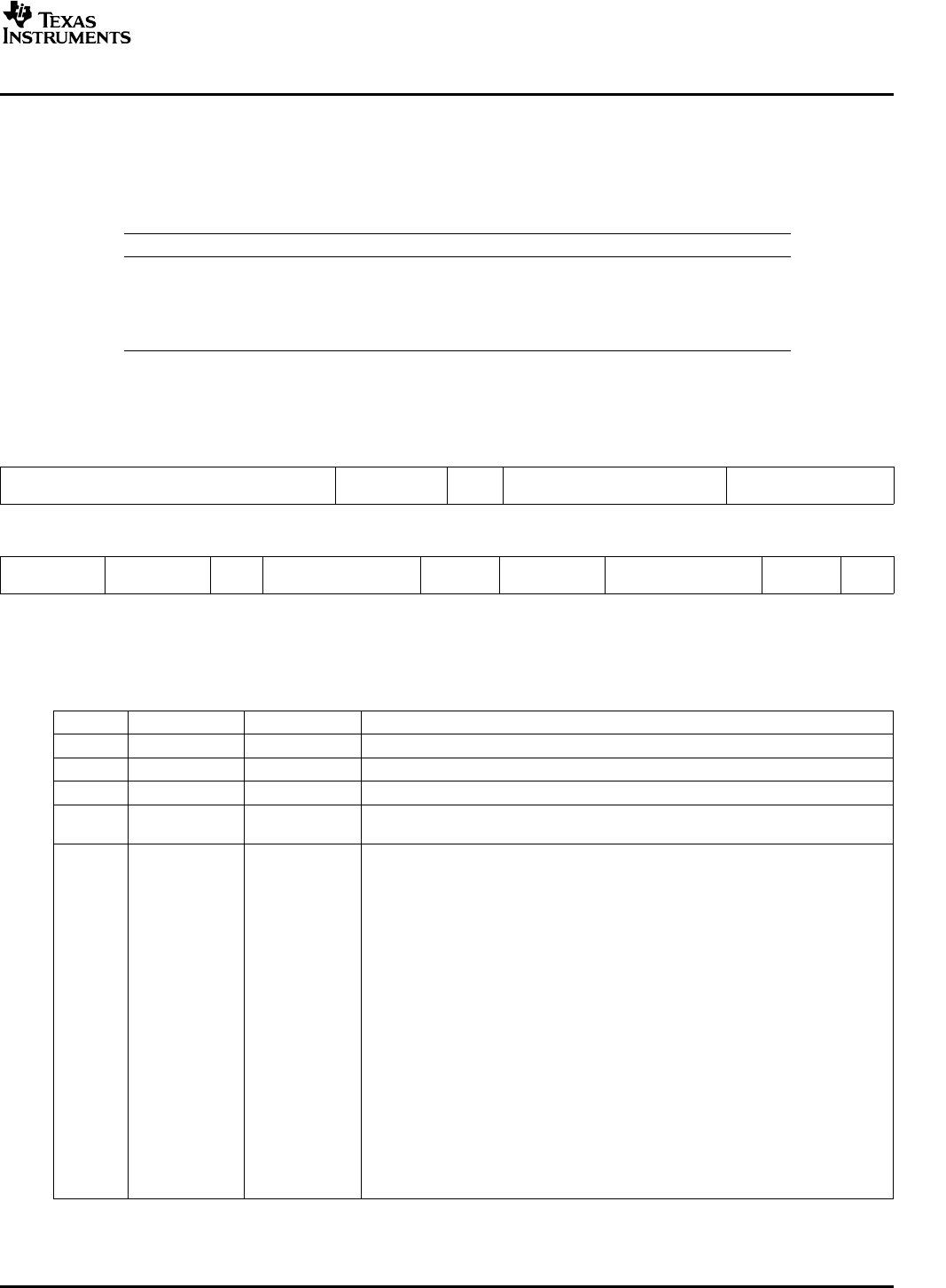

Figure74.SERDESReceiveChannelConfigurationRegistern(SERDES_CFGRXn_CNTL)

312625242322191816

Reserved

Reserved—EQCDR

(write0s)

R-0R/W-0R-0R/W-0R/W-0

15141312111087654210

TERM—

LOSALIGN—INVPAIRRATEBUSWIDTHENRX

(write001b)(write0)

R/W-0R/W-0R-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=Valueafterreset

Table57.SERDESReceiveChannelConfigurationRegistern(SERDES_CFGRXn_CNTL)Field

Descriptions

BitFieldValueDescription

31–26Reserved000000bTheseread-onlybitsreturn0swhenread.

25–24Reserved00bAlwayswrite0stothesereservedbits.

23Reserved0Thisread-onlybitreturns0whenread.

22–19EQ0000b–1111bEqualizer.Enablesandconfigurestheadaptiveequalizertocompensateforloss

inthetransmissionmedia.Fortheselectablevalues,seeTable58.

18–16CDRClock/datarecovery.Configurestheclock/datarecoveryalgorithm.

000bFirstorder.Phaseoffsettrackingupto±488ppm.

001bSecondorder.Highestprecisionfrequencyoffsetmatchingbutpoorestresponse

tochangesinfrequencyoffset,andlongestlocktime.Suitableforuseinsystems

withfixedfrequencyoffset.

010bSecondorder.Mediumprecisionfrequencyoffsetmatching,frequencyoffset

changeresponse,andlocktime.

011bSecondorder.Bestresponsetochangesinfrequencyoffsetandfastestlocktime,

butlowestprecisionfrequencyoffsetmatching.Suitableforuseinsystemswith

spreadspectrumclocking.

100bFirstorderwithfastlock.Phaseoffsettrackingupto±1953ppminthepresenceof

..10101010..trainingpattern,and±448ppmotherwise.

101bSecondorderwithfastlock.Aspersetting001,butwithimprovedresponseto

changesinfrequencyoffsetwhennotclosetolock.

110bSecondorderwithfastlock.Aspersetting010,butwithimprovedresponseto

changesinfrequencyoffsetwhennotclosetolock.

111bSecondorderwithfastlock.Aspersetting011,butwithimprovedresponseto

changesinfrequencyoffsetwhennotclosetolock.

SPRUE13A–September2006SerialRapidIO(SRIO)125

SubmitDocumentationFeedback