www.ti.com

SRIOFunctionalDescription

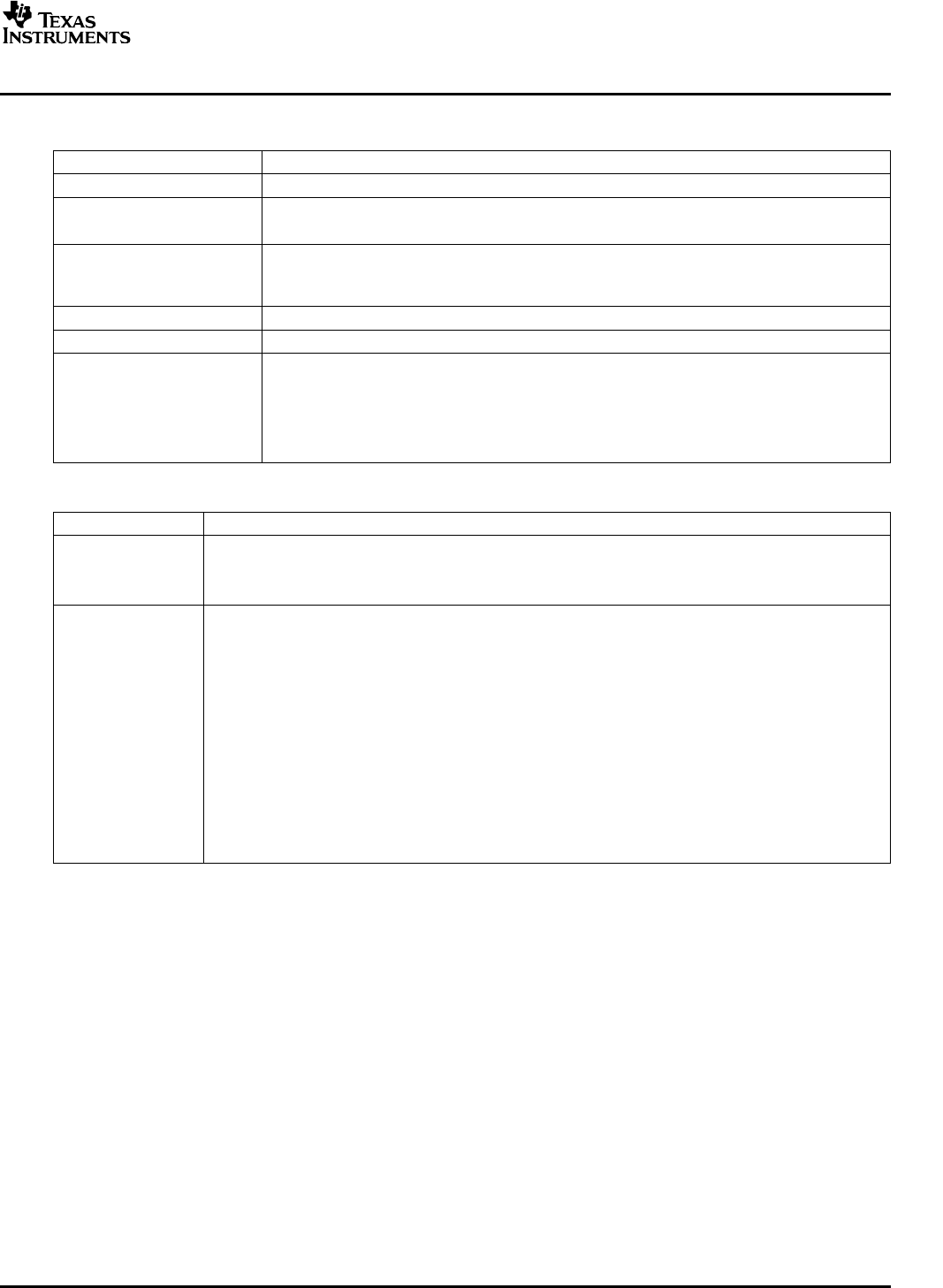

Table14.LSUControl/CommandRegisterFields(continued)

LSURegisterFieldRapidIOPacketHeaderField

DestIDRapidIOdestinationIDfieldspecifyingthetargetdevice.

PacketType4MSBs:4-bitftypefieldforallpackets

4LSBs:4-bittransfieldforpackettypes2,5,and8

OutPortIDNotavailableinRapidIOheader.

Indicatestheoutputportnumberforthepackettobetransmittedfrom.SpecifiedbytheCPU

alongwithNodeID.

DrbllInfoRapidIOdoorbellinfofieldfortype10packets.(seeTable23)

HopCountRapidIOhop_countfieldspecifiedforType8Maintenancepackets.

InterruptReqNotavailableinRapidIOheader.

CPUcontrolledrequestbitusedforinterruptgeneration.Typicallyusedinconjunctionwith

non-postedcommandstoalerttheCPUwhentherequesteddata/statusispresent.

0-Aninterruptisnotrequesteduponcompletionofcommand

1-Aninterruptisrequesteduponcompletionofcommand

Table15.LSUStatusRegisterFields

LSURegisterFieldFunction

BSYIndicatesstatusofthecommandregisters.

0-Commandregistersareavailable(writable)fornextsetoftransferdescriptors

1-Commandregistersarebusywithcurrenttransfer

CompletionCodeIndicatesthestatusofthependingcommand.

000b–Transactioncomplete,noerrors(Posted/Non-posted)

001b–TransactiontimeoutoccurredonNon-postedtransaction

010b–Transactioncomplete,packetnotsentduetoflowcontrolblockade(Xoff)

011b–Transactioncomplete,non-postedresponsepacket(type8and13)containedERRORstatus,or

responsepayloadlengthwasinerror

100b–Transactioncomplete,packetnotsentduetounsupportedtransactiontypeorinvalidprogramming

encodingforoneormoreLSUregisterfields

101b–DMAdatatransfererror

110b–RetryDOORBELLresponsereceived,orAtomicTest-and-swapwasnotallowed(semaphorein

use)

111b–Transactioncomplete,packetnotsentduetounavailableoutboundcreditatgivenpriority

(1)

(1)

Statusavailableonlywhenbusy(BSY)signal=0.

FourLSUregistersetsexist.Thisallowsfouroutstandingrequestsforalltransactiontypesthatrequirea

response(i.e.,non-posted).Formulti-coredevices,softwaremanagestheusageoftheregisters.A

sharedconfigurationbusaccessesallregistersets.AsinglecoredevicecanutilizeallfourLSUblocks.

Figure13showsthetimingdiagramforaccessingtheLSUregisters.Thebusy(BSY)signalisdeasserted.

LSUn_REG1iswrittenonconfigurationbusclockcycleT0,LSUn_REG2iswrittenoncycleT1,

LSUn_REG3iswrittenoncycleT2,andLSUn_REG4iswrittenoncycleT3.Thecommandregister

LSUn_REG5iswrittenoncycleT4.TheextendedaddressfieldinLSUn_REG0isassumedtobeconstant

inthisexample.Uponcompletionofthewritetothecommandregister(nextclockcycleT5),theBSY

signalisasserted,atwhichpointtheprecedingcompletioncodeisinvalidandaccessestotheLSU

registersarenotallowed.Oncethetransactioncompletes(eitherasasuccessfultransmission,or

unsuccessfully,suchasflowcontrolpreventionorresponsetimeout)andanyrequiredinterruptservice

routineiscompleted,theBSYsignalisdeassertedandthecompletioncodebecomesvalidandthe

registersareaccessibleagain.

SPRUE13A–September2006SerialRapidIO(SRIO)37

SubmitDocumentationFeedback