www.ti.com

SRIOFunctionalDescription

TheclockrecoveryalgorithmslistedintheCDRbitsoperatetoadjusttheclocksusedtosamplethe

receivedmessagesothatthedatasamplesaretakenmidwaybetweendatatransitions.Thesecondorder

algorithmcanbeoptionallydisabled,andbothcanbeconfiguredtooptimizetheirdynamics.Both

algorithmsusethesamebasictechniquefordeterminingwhetherthesamplingclockisideallyplaced,and

ifnotwhetheritneedstobemovedearlierorlater.Whentwocontiguousdatasamplesaredifferent,the

phasesamplebetweenthetwoisexamined.Eightdatasamplesandninephasesamplesaretakenwith

eachresultcountedasavotetomovethesamplepointeitherearlierorlater.Theseeightdatabits

constitutethevotingwindow.Theeightvotesarethencounted,andanactiontoadjustthepositionofthe

samplingclockoccursifthereisamajorityofearlyorlatevotes.Thefirstorderalgorithmmakesasingle

phaseadjustmentpermajorityvote.Thesecondorderalgorithmactsrepeatedlyaccordingtothenet

differencebetweenearlyandlatemajorityvotes,therebyadjustingfortherateofchangeofphase.

SettingtheALIGNfieldto01enablesalignmenttotheK28commasymbolsincludedinthe8b:10bdata

encodingschemedefinedbytheIEEEandemployedbynumeroustransmissionstandards.Forsystems

whichcannotusecommabasedsymbolalignment,thesinglebitalignmentjogcapabilityprovidesa

meanstocontrolthesymbolrealignmentfeaturesofthereceiverdirectlyfromlogicimplementedinthe

ASICcore.Thislogiccanbedesignedtosupportwhateveralignmentdetectionprotocolisrequired.

TheEQbitsallowforenablingandconfiguringtheadaptiveequalizerincorporatedinallofthereceive

channels,whichcancompensateforchannelinsertionlossbyattenuatingthelowfrequencycomponents

withrespecttothehighfrequencycomponentsofthesignal,therebyreducinginter-symbolinterference.

Abovethezerofrequency,thegainincreasesat6dB/octaveuntilitreachesthehighfrequencygain.When

enabled,thereceiverequalizationlogicanalyzesdatapatternsandtransitiontimestodeterminewhether

thelowfrequencygainoftheequalizershouldbeincreasedordecreased.Forthefullyadaptivesetting

(EQ=0001),ifthelowfrequencygainreachestheminimumvalue,thezerofrequencyisthenreduced.

Likewise,ifitreachesthemaximumvalue,thezerofrequencyisthenincreased.Thisdecisionlogicis

implementedasavotingalgorithmwitharelativelylonganalysisinterval.Theslowtimeconstantthat

resultsreducestheprobabilityofincorrectdecisionsbutallowstheequalizertocompensateforthe

relativelystableresponseofthechannel.

•Noadaptiveequalization.Theequalizerprovidesaflatresponseatthemaximumgain.Thissetting

maybeappropriateifjitteratthereceiveroccurspredominantlyasaresultofcrosstalkratherthan

frequencydependentloss.

•Fullyadaptiveequalization.Boththelowfrequencygainandzeropositionoftheequalizerare

determinedalgorithmicallybyanalysingthedatapatternsandtransitionpositionsinthereceiveddata.

Thissettingshouldbeusedformostapplications.

•Partiallyadaptiveequalisation.Thelowfrequencygainoftheequalizerisdeterminedalgorithmicallyby

analysingthedatapatternsandtransitionpositionsinthereceiveddata.Thezeropositionisfixedin

oneofeightzeropositions.Foranygivenapplication,theoptimalsettingisafunctionoftheloss

characteristicsofthechannelandthespectraldensityofthesignalaswellasthedatarate,which

meansitisnotpossibletoidentifythebestsettingbydataratealone,althoughgenerallyspeaking,the

lowerthelinerate,thelowerthezerofrequencythatwillberequired.

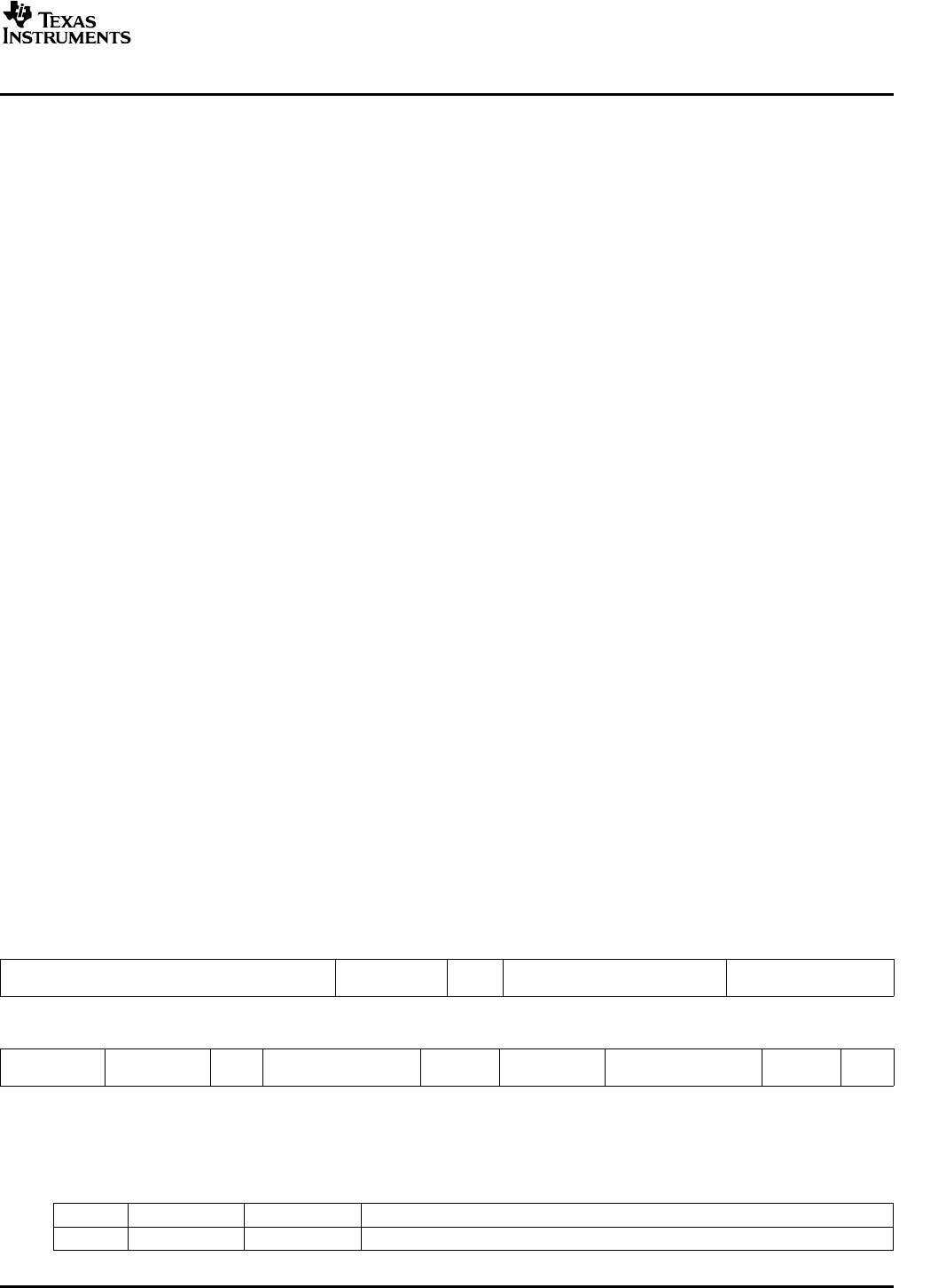

Figure10.SERDESReceiveChannelConfigurationRegistern(SERDES_CFGRXn_CNTL)

312625242322191816

Reserved

Reserved—EQCDR

(write0s)

R-0R/W-0R-0R/W-0R/W-0

15141312111087654210

TERM—

LOSALIGN—INVPAIRRATEBUSWIDTHENRX

(write001b)(write0)

R/W-0R/W-0R-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=Valueafterreset

Table9.SERDESReceiveChannelConfigurationRegistern(SERDES_CFGRXn_CNTL)Field

Descriptions

BitFieldValueDescription

31–26Reserved000000bTheseread-onlybitsreturn0swhenread.

SPRUE13A–September2006SerialRapidIO(SRIO)31

SubmitDocumentationFeedback