www.ti.com

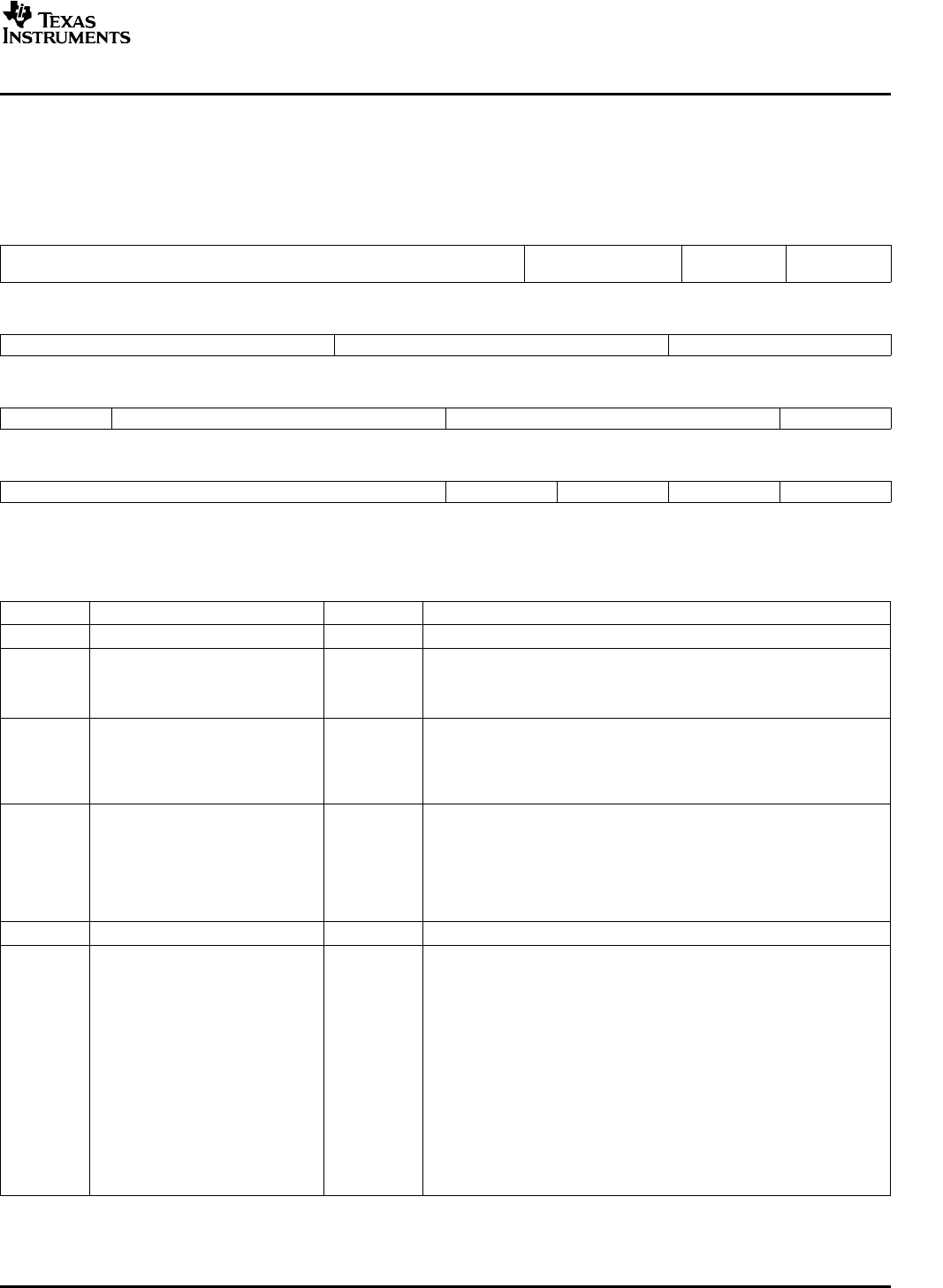

5.4PeripheralSettingsControlRegister(PER_SET_CNTL)

SRIORegisters

Theperipheralsettingscontrolregister(PER_SET_CNTL)isshowninFigure65anddescribedin

Table43.Foradditionalprogramminginformation,seeSection2.3.12.

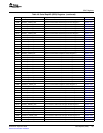

Figure65.PeripheralSettingsControlRegister(PER_SET_CNTL)(AddressOffset0020h)

3127262524

SW_MEM_SLEEP_BOOT_

ReservedLOOPBACK

OVERRIDECOMPLETE

R-0R/W-1R/W-0R/W-0

232120181716

ReservedTX_PRI2_WMTX_PRI1_WM

R-0R/W-01hR/W-02h

1514121198

TX_PRI1_WMTX_PRI0_WMCBA_TRANS_PRI1X_MODE

R/W-02hR/W-03hR/W-0R/W-0

743210

PRESCALER_SELECTENPLL4ENPLL3ENPLL2ENPLL1

R/W-0R/W-0R/W-0R/W-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=Valueafterreset

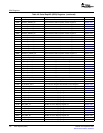

Table43.PeripheralSettingsControlRegister(PER_SET_CNTL)FieldDescriptions

BitFieldValueDescription

31–27Reserved00000bTheseread-onlybitsreturn0swhenread.

26SW_MEM_SLEEP_OVERRIDESoftwarememorysleepoverride

0Memoriesareputinsleepmodewhileinshutdown

1Memoriesarenotputinsleepmodewhileinshutdown

25LOOPBACKLoopbackmode

0Normaloperation

1Loopbackmode.Transmitdatatoreceiveonthesameport.Packet

dataisloopedbackinthedigitaldomainbeforetheSERDESmacros.

24BOOT_COMPLETEControlsabilitytowriteanyregisterduringinitialization.Italsoincludes

readonlyregistersduringnormalmodeofoperationthathave

applicationdefinedresetvalue.

0Writetoread-onlyregistersenabled

1Writetoread-onlyregistersdisabled.Usuallytheboot_completeis

assertedonceafterresettodefinepoweronconfiguration.

23–21Reserved000bTheseread-onlybitsreturn0swhenread.

20–18TX_PRI2_WM000b–111bTransmitcreditthreshold.SetstherequirednumberoflogicallayerTX

buffersneededtosendpriority2packetsacrosstheUDI.Thisisvalid

forallportsin1xmodeonly.

Requiredbuffercountfortransmitcreditthreshold2value

(TX_PRI2_WM):

•000→8,7,6,5,4,3,2,1(effectivelyletsallofthisprioritypass)

•001→8,7,6,5,4,3,2

•010→8,7,6,5,4,3

•011→8,7,6,5,4

•100→8,7,6,5

•101→8,7,6

•110→8,7

•111→8

SPRUE13A–September2006SerialRapidIO(SRIO)113

SubmitDocumentationFeedback