www.ti.com

SRIOFunctionalDescription

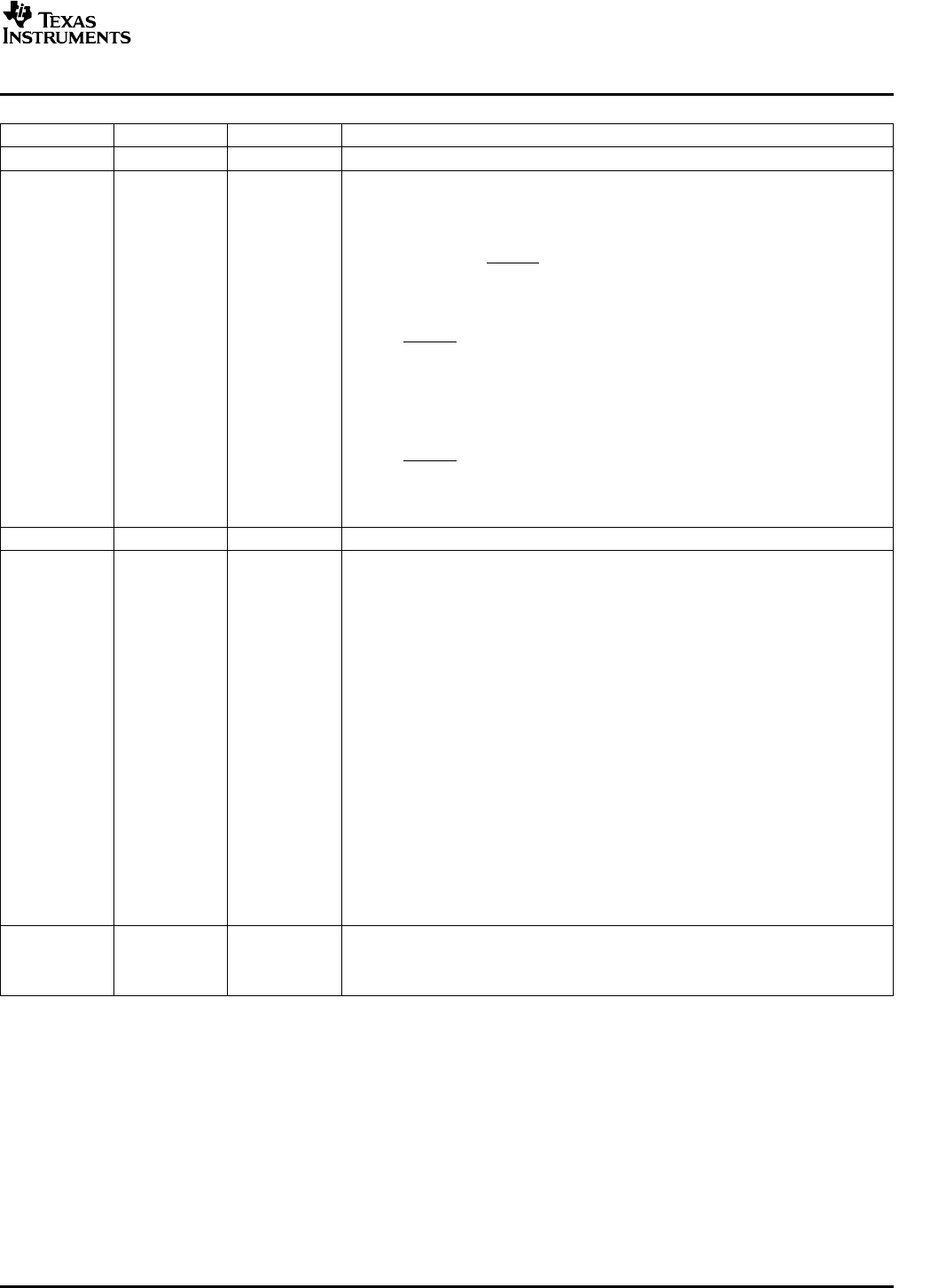

Table5.SERDESMacroConfigurationRegister0(SERDES_CFG0_CNTL)FieldDescriptions

BitFieldValueDescription

31–10Reserved0000hReserved

9–8LBLoopbandwidth.Specifyloopbandwidthsettings.Jitteronthereferenceclockwill

degradeboththetransmiteyeandreceiverjittertolerancetherebyimpairingsystem

performance.PerformanceoftheintegratedPLLcanbeoptimizedaccordingtothe

jittercharacteristicsofthereferenceclockviatheLBfield.

00bFrequencydependentbandwidth.ThePLLbandwidthissettoatwelfthofthe

frequencyofRIOCLK/RIOCLK.Thissettingissuitableformostsystemsthatinputthe

referenceclockviaalowjitterinputcell,andisrequiredforstandardscompliance

01bReserved

10bLowbandwidth.ThePLLbandwidthissettoatwentiethofthefrequencyof

RIOCLK/RIOCLK,or3MHz(whicheverislarger).Insystemswherethereference

clockisdirectlyinputviaalowjitterinputcell,butisoflowerquality,thissettingmay

offerbetterperformance.Itwillreducetheamountofreferenceclockjittertransferred

throughthePLL.However,italsoincreasesthesusceptibilitytoloopnoisegenerated

withinthePLLitself.Itisdifficulttopredictwhethertheimprovementintheformerwill

morethanoffsetthedegradationinthelatter.

11bHighbandwidth.ThePLLbandwidthissettoaeighthofthefrequencyof

RIOCLK/RIOCLK.Thisisthesettingappropriateforsystemswherethereference

clockiscleanedthroughanultralowjitterLC-basedPLL.Standardscompliancewill

beachievedevenifthereferenceclockinputtothecleanerPLLisoutsidethe

specificationforthestandard.

7–6Reserved00hReserved

5–1MPYPLLmultiply.SelectPLLmultiplyfactorsbetween4and60.

00000b4x

00001b5x

00010b6x

00011bReserved

00100b8x

00101b10x

00110b12x

00111b12.5x

01000b15x

01001b20x

01010b25x

01011bReserved

01100bReserved

01111bReserved

1xxxxbReserved

0ENPLLEnablePLL

0PLLdisabled

1PLLenabled

BasedontheMPYvalue,thelinerateversusPLLoutputclockfrequencycanbecalculated.Thisis

summarizedinTable6.

SPRUE13A–September2006SerialRapidIO(SRIO)29

SubmitDocumentationFeedback