www.ti.com

2.3.10.3SoftwareShutdownDetails

2.3.11Emulation

SRIOFunctionalDescription

Powerconsumptionisminimizedforalllogicalblocksthatareinshutdown.Inadditiontosimplyasserting

theappropriateresetsignaltoeachlogicalblockwithintheperipheral,clocksaregatedofftothe

correspondinglogicalblockaswell.Clocksareallowedtorunfor32clockcycles,whichisnecessaryto

fullyreseteachlogicalblock.Whentheappropriatelogicalblockisfullyreset,theclockinputtothat

subblockisgatedoff.WhensoftwareassertsGBL_EN/BLKn_ENtoreleasethelogicalblockfromreset,

theclocksareun-gatedandtheGBL_EN_STAT/BLKn_EN_STATbit(s)indicateavalueof1b.

Note:TheBLK_ENbitsallowyoutoshutdownandgateclockstounusedportionsofthelogic,

whileotherpartsoftheperipheralcontinuetooperate.Whenshuttingdownanindividual

block,ifTXUandRXUqueuesarenottorndowncorrectly,theDMAbuscouldhang.For

example,settingBLK3_EN=0(disablingtheTXU)beforeateardownofthequeuecould

causeanyoutstandingDMArequestreturnedtotheperipheralfortheTXUtohangthe

bus.

WhenusingtheGBL_ENtoshutdown/resettheentireperipheral,itisimportanttofirststopall

master-initiatedcommandsontheDMAbusinterface.Forexample,iftheGBL_ENisassertedinthe

middleofaDMAtransferfromtheperipheral,thiscouldhangthebus.Theproceduretofollowis:

1.StopallRapidIOsourcetransactions,includingLSUandTXUoperations.ThefourLSUblocksshould

indiciateaBSYstatusof0b(offsets0418h,0438h,0458h,0478h).IfanEDMAchannelisusedfor

drivingtheLSU,itmustbestoppedtopreventnew/additionaltransfers.Thisprocedureisoutsidethe

scopeofthisspecification.TeardownoftheTXUqueuesisaccomplishedbywriting0000FFFFhto

RIO_TX_QUEUE_TEAR_DOWN(offset0700h).Hardwarewillthenteardownthequeuesandclear

thesebitsautomaticallywhentheteardowniscomplete.

2.StopallRapidIOmessagereceive,RXU,operations.TeardownoftheRXUqueuesisaccomplishedby

writing0000FFFFhtoRIO_RX_QUEUE_TEAR_DOWN(offset0740h).Hardwarewillthenteardown

thequeuesandclearthesebitsautomaticallywhencomplete.

3.Onceteardowniscomplete,clearthePERENbitoftheRIO_PCR(offset0004h)tostopallnewlogical

layertransactions.

4.Wait1secondtofinishanycurrentDMAtransfer.

5.DeassertGBL_EN(offset0030h).

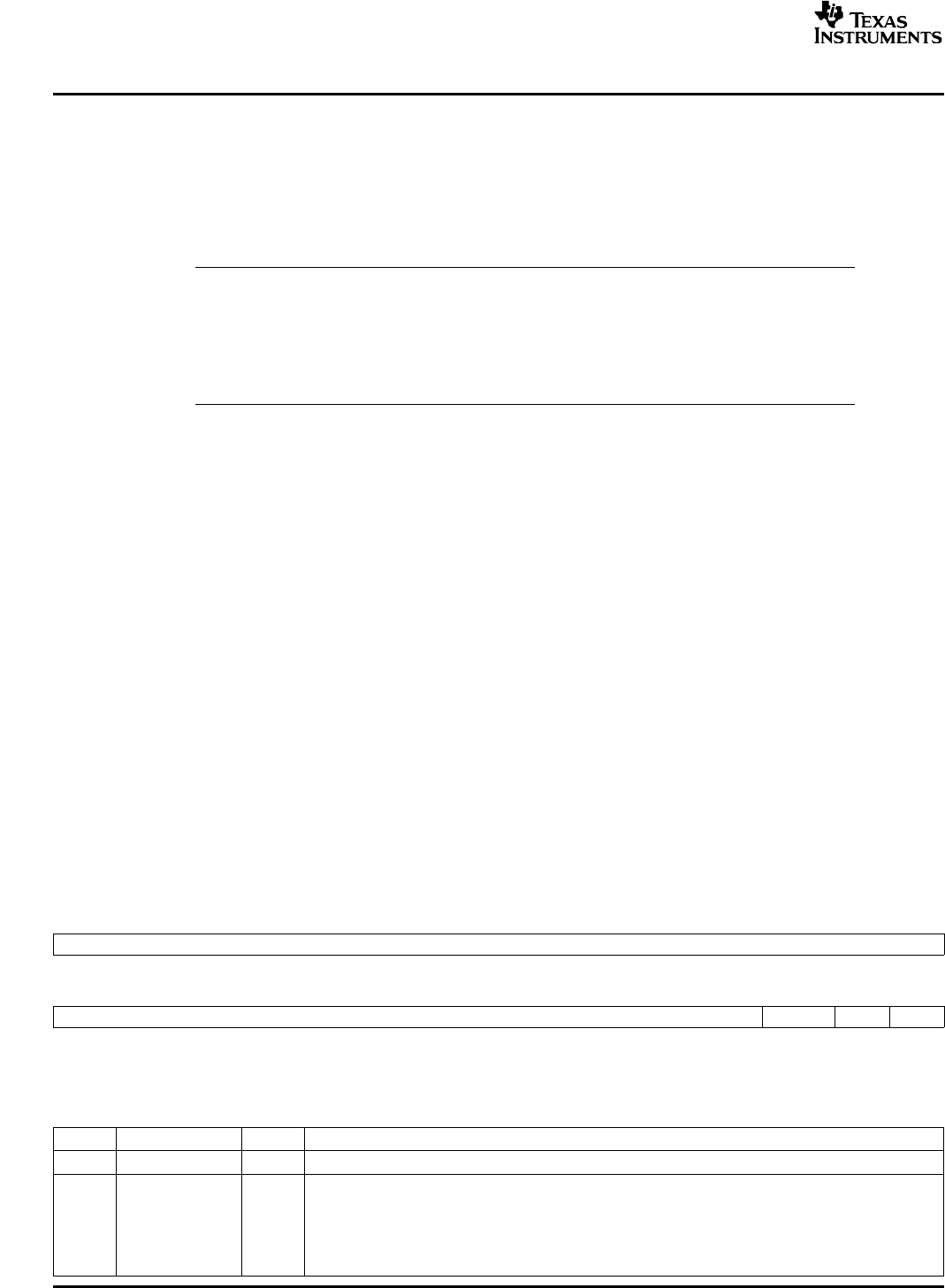

ExpectedbehaviorduringemulationhaltiscontrolledwithintheperipheralbytheSOFTandFREEbitsof

theperipheralcontrolregister(PCR).ThesebitsareshowninFigure40anddescribedinTable29.

Figure40.PeripheralControlRegister(PCR)-AddressOffset0004h

3116

Reserved

R-0

153210

ReservedPERENSOFTFREE

R-0R/W-0R/W-0R/W-1

LEGEND:R/W=Read/Write;R=Readonly;-n=Valueafterreset

Table29.PeripheralControlRegister(PCR)FieldDescriptions

BitFieldValueDescription

31–3Reserved0Theseread-onlybitsreturn0swhenread.

2PERENPeripheralenable.Controlstheflowofdatainthelogicallayeroftheperipheral.Asaninitiator,it

willpreventTXtransactiongeneration;asatarget,itwilldisableincomingrequests.Thisshouldbe

thelastenablebittotogglewhenbringingthedeviceoutofresettobeginnormaloperation.

0Dataflowcontrolisdisabled.

1Dataflowcontrolisenabled.

74SerialRapidIO(SRIO)SPRUE13A–September2006

SubmitDocumentationFeedback