www.ti.com

5.92PortIPModeCSR(SP_IP_MODE)

SRIORegisters

TheportIPmodeCSR(SP_IP_MODE)isshowninFigure155anddescribedinTable177.Foradditional

programminginformation,seeSection2.3.13.2.

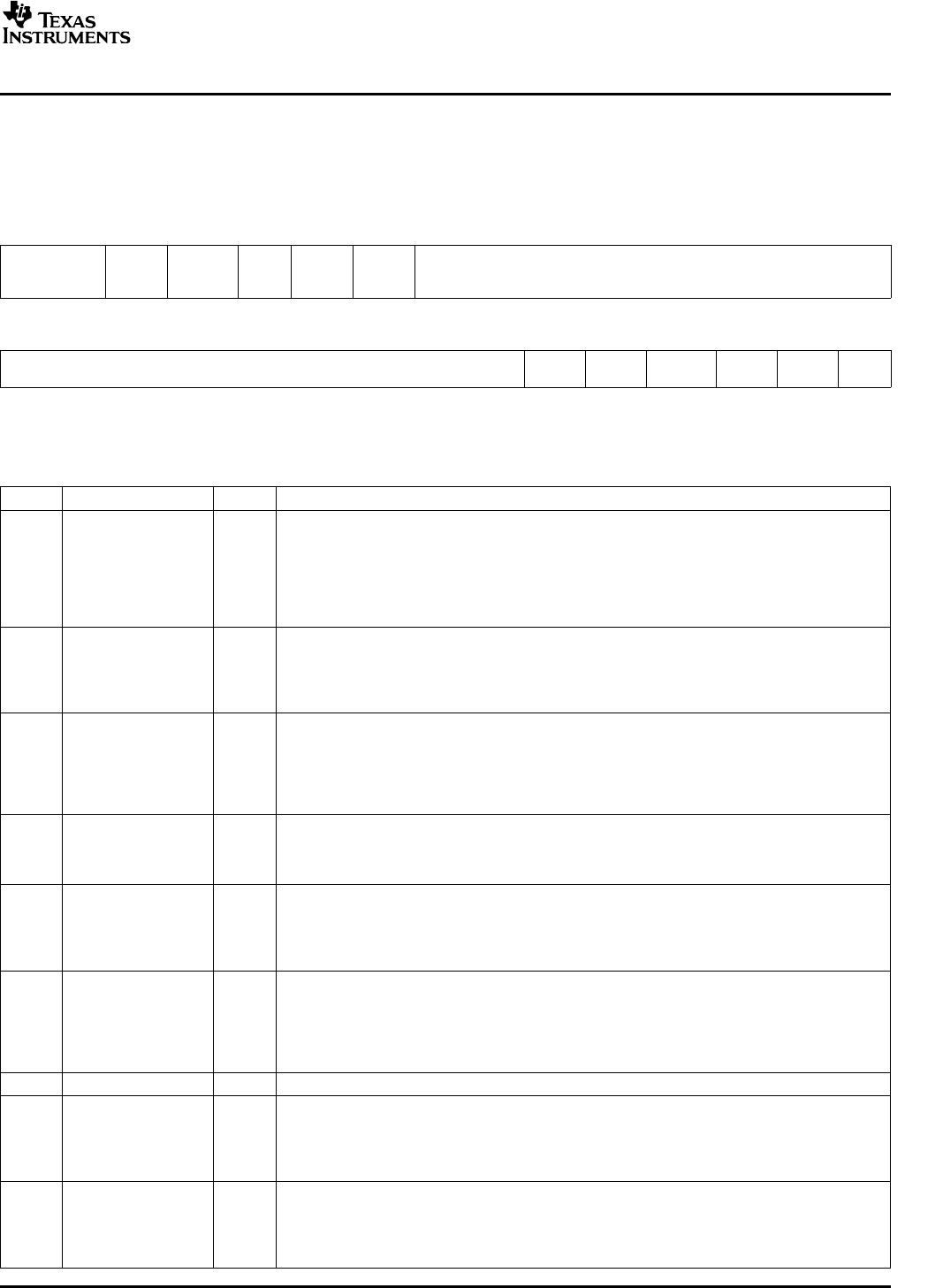

Figure155.PortIPModeCSR(SP_IP_MODE)-AddressOffset12004h

313029282726252416

IDLE_TX_

PW_TGT_SELF_

SP_MODEERR_FIFO_Reserved

DISID_DISRST

DISBYPASS

R/W-0R/W-0R/W-0R/W-0R-0R/W-0R-0

156543210

MLTC_MLTC_RST_RST_PW_PW_

Reserved

ENIRQENCSENIRQ

R-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=Valueafterreset

Table177.PortIPModeCSR(SP_IP_MODE)FieldDescriptions

BitFieldValueDescription

31–30SP_MODESRIOportIPmodeofoperation

00bRapidIOPhysicalLayer1x/4xLP-SerialSpecification

01b4ports(1xmodeeach)

10bReserved

11bReserved

29IDLE_ERR_DISIdleerrorcheckingdisable

0Errorcheckingenabled(default),only|K|,|A|and|R|charactersareavailable.Ifinputreceives

anyothercharactersinidlesequence,itshouldentertheInput-Error-stoppedstate.

1Errorcheckingdisabled,allnotidleorinvalidcharactersduringidlesequenceareignored

28TX_FIFO_BYPASSTransmitFIFObypass

0TheTX_FIFOisoperational(default)

1TheTX_FIFOisbypassed.Thetxbclkandthesys_clkmustbelockedduringoperation,butthe

phasevariationupto1clockcycleisallowable.The4deepFIFOisusedtoaccommodatethe

phasedifference.

27PW_DISPort-writeerrorreportingdisable.

0EnablePort-WriteErrorreporting(default)

1DisablePort-WriteErrorreporting

26TGT_ID_DISDestinationIDDecodeDisable-Definitionofpacketacceptancebythephysicallayer.

0PacketacceptedifDestID=BaseID.WhenDestIDisnotequaltoBaseID,thepacketis

ignored;i.e.,itisacceptedbyRapidIOportbutisnotforwardedtologicallayer.

1PacketacceptedwithanyDestIDandforwardedtothelogicallayer.

25SELF_RSTSelfresetinterruptenable,when4link-requestresetcontrolsymbolsareaccepted.

0Selfresetinterruptdisabled(default),interruptsignalisasserted

1Selfresetinterruptenabled,theresetsignalisassertedbytheresetcontroller.Whenthe

SELF_RSTissetto1,theSERDESmacroresetsandallregistervaluesfromaddressoffset

1000handhigherarereturnedtodefaultvalue.Allinitializedvaluesarelost.

24–6Reserved0Theseread-onlybitsreturn0swhenread.

5MLTC_ENMulticast-EventInterruptEnable.Ifenabled,theinterruptsignalisHighwhenthe

Multicast-Eventcontrolsymbolisreceivedbyanyport.

0Multicastinterruptdisable

1Multicastinterruptenable

4MLTC_IRQMulticast-eventinterruptstatus.Onceset,theMLTC_IRQbitremainssetuntilsoftwarewritesa

1toit.Themltc_irqoutputsignalisdrivenbythisbit.

0Themulticasteventcontrolsymbolhasnotbeenreceivedbyanyoftheports.

1Themulticast-eventcontrolsymbolhasbeenreceivedbyoneoftheports.

SPRUE13A–September2006SerialRapidIO(SRIO)231

SubmitDocumentationFeedback