www.ti.com

4InterruptConditions

4.1CPUInterrupts

4.2GeneralDescription

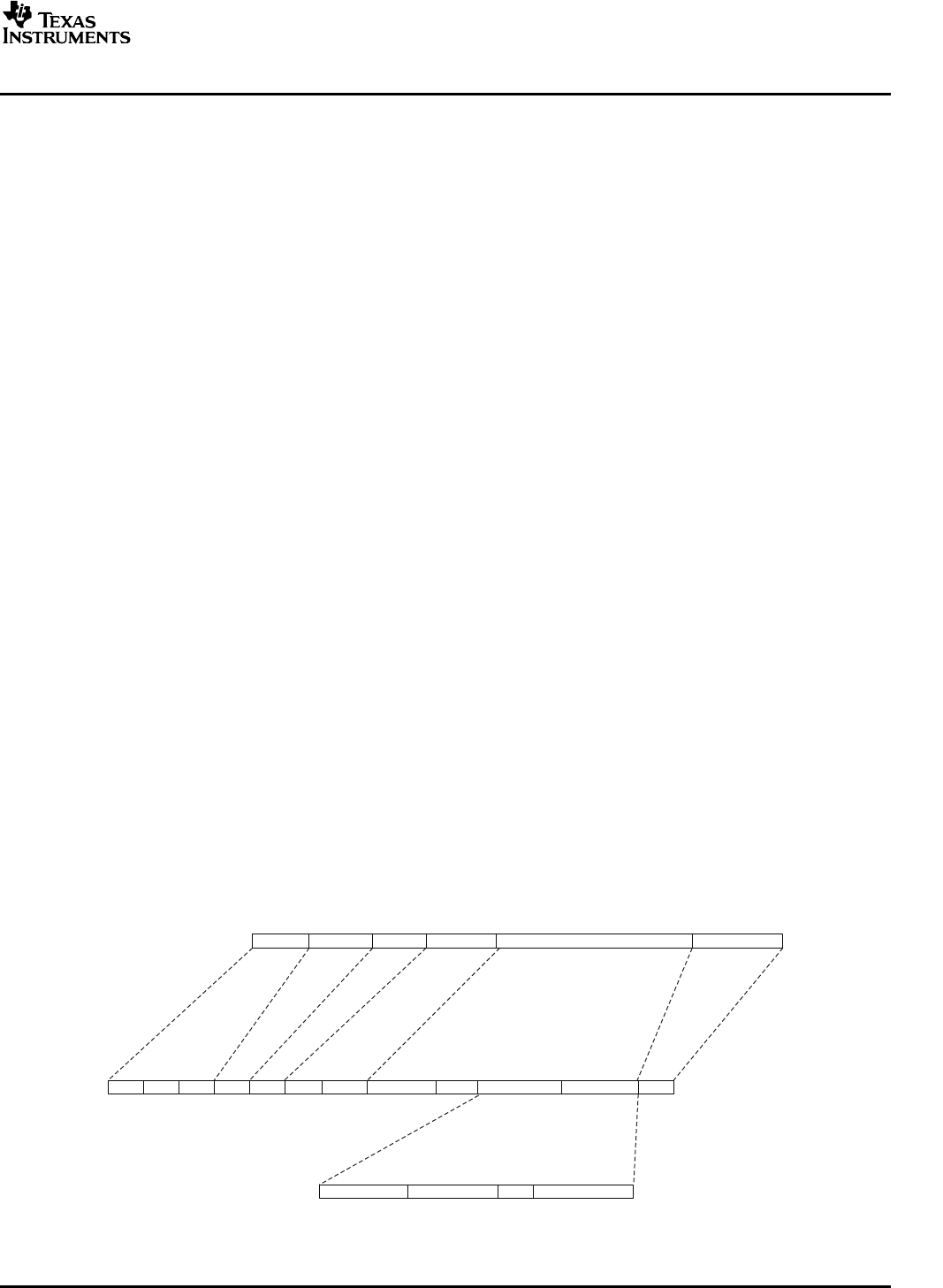

acklD rsv prio tt 1010 destID sourcelD Reserved srcTID

Reserved DoorbellReg# rsv

Doorbellbit

CRC

PHYLOGTRALOGTRAPHY

5 3 2 2 4 8 8 8 8

9 2

1

4

16

1632

16

4

2

10

info(msb)

8

info(lsb)

8

InterruptConditions

ThissectiondefinestheCPUinterruptcapabilitiesandrequirementsoftheperipheral.

ThefollowinginterruptsaresupportedbytheRIOperipheral.

•Errorstatus:Eventindicatingthatarun-timeerrorwasreached.TheCPUshouldreset/resynchronize

theperipheral.

•Criticalerror:Eventindicatingthatacriticalerrorstatewasreached.TheCPUshouldresetthesystem.

•CPUservicing:EventindicatingthattheCPUshouldservicetheperipheral.

TheRIOperipheraliscapableofgeneratingvarioustypesofCPUinterrupts.Theinterruptsservetwo

generalpurposes:errorindicationandservicingrequests.

SinceRapidIOisapacketorientedinterface,theperipheralmustrecognizeandrespondtoinbound

signalsfromtheserialinterface.TherearenoGPIOorexternalpinsusedtoindicateaninterruptrequest.

Thus,theinterruptrequestsaresignaledeitherbyanexternalRapidIOdevicethroughthepacket

protocolsdiscussedasfollows,oraregeneratedinternallybytheRIOperipheral.

CPUservicinginterruptslagbehindthecorrespondingdata,whichwasgenerallytransferredfroman

externalprocessingelementintolocalL2memory.ThistransfercanuseamessagingordirectI/O

protocol.Whenthesingleormulti-packetdatatransferiscomplete,theexternalPE,ortheperipheral

itself,mustnotifythelocalprocessorthatthedataisavailableforprocessing.Toavoiderroneousdata

beingprocessedbythelocalCPU,thedatatransfermustcompletethroughtheDMAbeforetheCPU

interruptisserviced.Thisconditioncouldoccursincethedataandinterruptqueuesareindependentof

eachother,andDMAtransferscanstall.Toavoidthiscondition,alldatatransfersfromtheperipheral

throughtheDMAusewrite-with-responseDMAbuscommands,allowingtheperipheraltoalwaysbe

awarethatoutstandingtransfershavecompleted.InterruptsaregeneratedonlyafterallDMAbus

responsesarereceived.SinceallRapidIOpacketsarehandledsequentially,andsubmittedonthesame

DMApriorityqueue,theperipheralmustkeeptrackofthenumberofDMArequestssubmittedandthe

numberofresponsesreceived.Thus,asimplecounterwithintheperipheralensuresthatdatapackets

havearrivedinmemorybeforesubmittinganinterrupt.

ThesendingdeviceinitiatestheinterruptbyusingtheRapidIOdefinedDOORBELLmessage.The

DOORBELLpacketformatisshowninFigure45.TheDOORBELLfunctionalityisuser-defined.This

packettypeiscommonlyusedtoinitiateCPUinterrupts.ADOORBELLpacketisnotassociatedwitha

particulardatapacketthatwaspreviouslytransferred,sotheINFOfieldofthepacketmustbeconfigured

toreflecttheDOORBELLbittobeservicedforthecorrectTIDinfotobeprocessed.

Figure45.RapidIODOORBELLPacketforInterruptUse

SPRUE13A–September2006SerialRapidIO(SRIO)85

SubmitDocumentationFeedback