www.ti.com

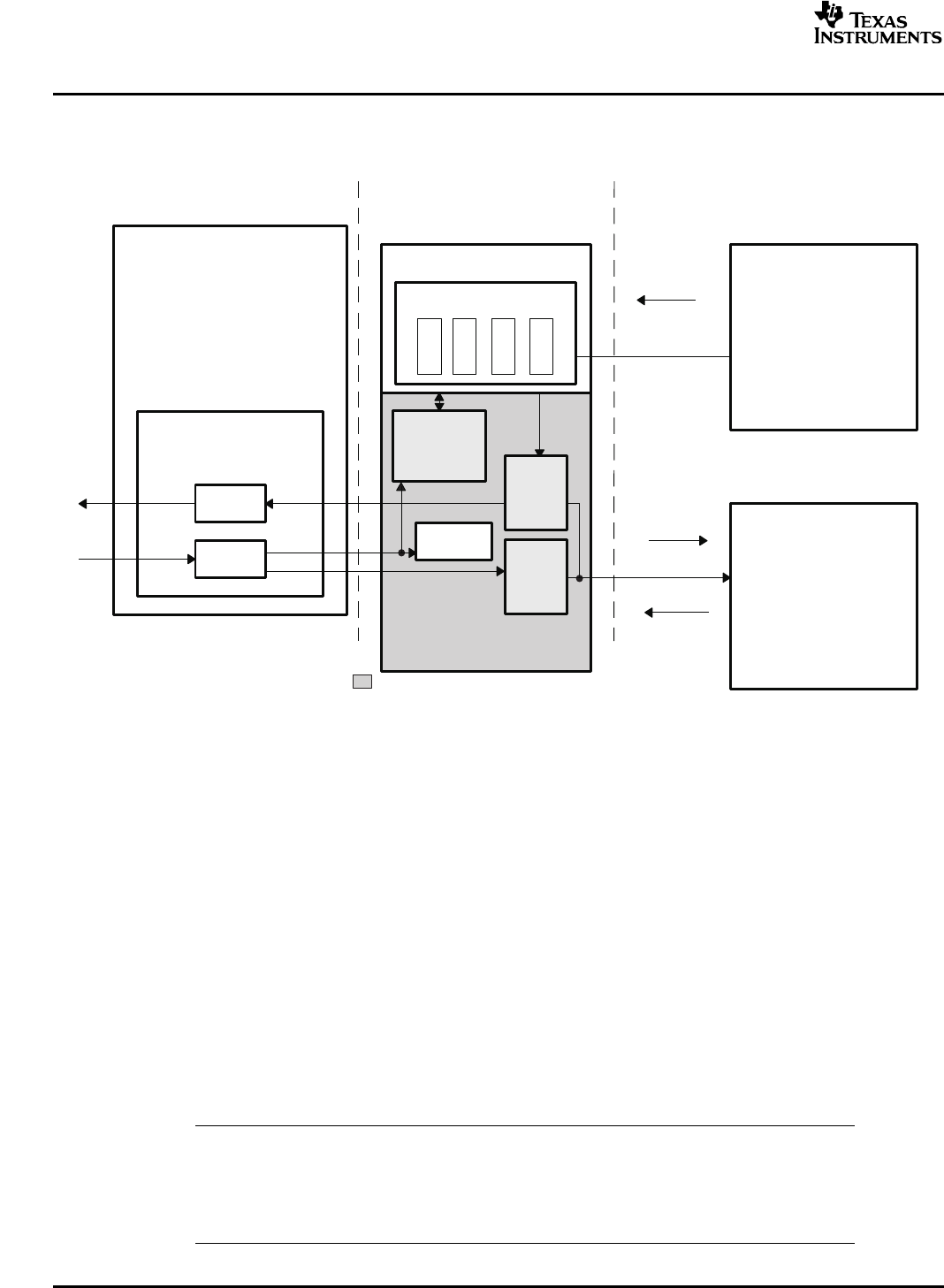

LSU2

LSU4

LSU3

LSU1

MMRcommand

UDI

Load/Storemodule

RapidIOtransport

andphysicallayers

Portxtransmission

FIFOqueues

TX

FIFO

RX

FIFO

Peripheralboundary

Configbus

access

Writetransfer

descriptors

CPU

I/O

pins

L2memory

=SharedresourceforCPPIandMAU

Shared

TX

buffer

Shared

RX

buffer

Response

timer

Control

and

arbitrator

DMA

request

DMA

response

2.3.3.2DirectI/OTXOperation

SRIOFunctionalDescription

Figure15.Load/StoreModuleDataFlowDiagram

WRITETransactions:

TheTXbuffersareimplementedinasingleSRAMandsharedbetweenmultiplecores.Astatemachine

arbitratesandassignsavailablebuffersbetweentheLSUs.WhentheDMAbusreadrequestis

transmitted,theappropriateTXbufferaddressisspecifiedwithinit.Thedatapayloadiswrittentothat

bufferthroughtheDMAbusresponsetransaction.Dependingonthearchitectureofthedevice,

interleavingofmulti-segmentedDMAbusresponsesfromtheDMAispossible.UponreceiptofaDMA

busreadresponsesegment,theunitchecksthecompletionstatusofthepayload.Notethatonlyone

payloadcanbecompletedinanysingleDMAbuscycle.TheLoad/Storemodulecanonlyforwardthe

packettotheTXFIFOafterthefinalpayloadbytefromtheDMAbusresponsehasbeenwrittenintothe

sharedTXbuffer.OncethepacketisforwardedtotheTXFIFO,thesharedTXbuffercanbereleasedand

madeavailableforanewtransaction.

TheTXbufferspaceisdynamicallysharedamongalloutgoingsources,includingtheLoad/Storemodule

andtheTXCPPI,aswellastheresponsepacketsfromRXCPPIandthememoryaccessunit(MAU).

Thus,thebufferspacememoryispartitionedtohandlepacketswithandwithoutpayloads.A4.5K-byte

bufferspaceisconfiguredtosupport16packetswithpayloadsupto256bytes,inadditionto16packets

withoutpayloads.TheSRAMisconfiguredasa128-bitwidetwoport,whichmatchestheUDIwidthofthe

TXFIFOs.

Note:The"UDI"("UserDefinedInterface")isareferencetotheinterfacebetween(a)the

SERDESandtheFIFOqueuesand(b)thelogicalbuffers,sharedbuffers,LSUandMAU

modules,responsetimer,andcontrollers(togetherknownasthe"UserApplication").UDI

couldalsobeknownasthe"logical/physicalinterface".Noactionisrequiredto"define"

thisinterface.

40SerialRapidIO(SRIO)SPRUE13A–September2006

SubmitDocumentationFeedback