www.ti.com

5.3PeripheralControlRegister(PCR)

SRIORegisters

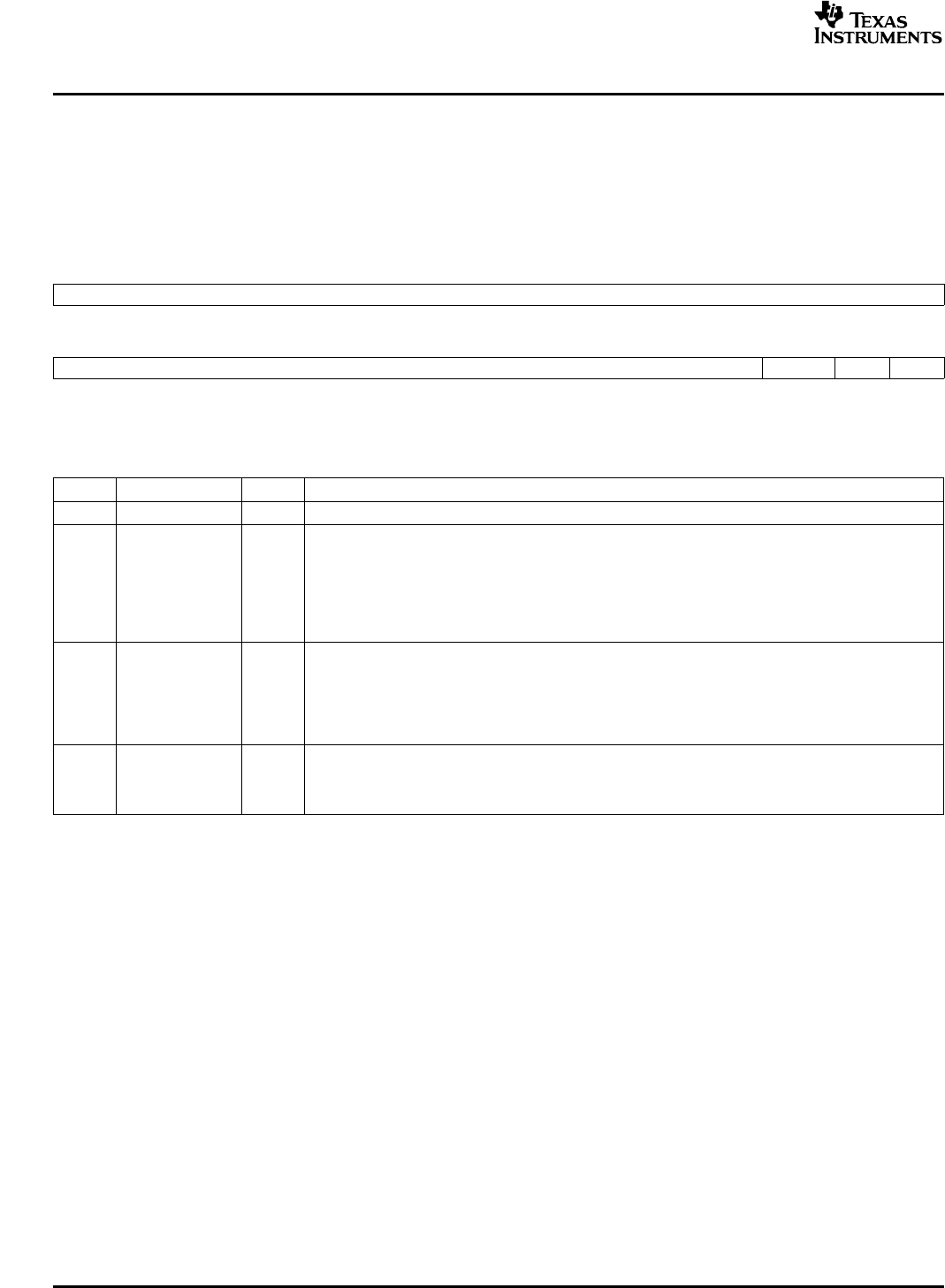

Theperipheralcontrolregister(PCR)containsabitthatenablesordisablesdataflowinthelogicallayer

oftheentireperipheral.Inaddition,thePCRhasemulationcontrolbitsthatcontroltheperipheralbehavior

duringemulationhalts.PCRisshowninFigure64anddescribedinTable42.Foradditionalprogramming

information,seeSection2.3.11.

Figure64.PeripheralControlRegister(PCR)-AddressOffset0004h

3116

Reserved

R-0

153210

ReservedPERENSOFTFREE

R-0R/W-0R/W-0R/W-1

LEGEND:R/W=Read/Write;R=Readonly;-n=Valueafterreset

Table42.PeripheralControlRegister(PCR)FieldDescriptions

BitFieldValueDescription

31–3Reserved0Theseread-onlybitsreturn0swhenread.

2PERENPeripheralflowcontrolenable.Controlstheflowofdatainthelogicallayeroftheperipheral.Asan

initiator,itwillpreventTXtransactiongeneration;asatarget,itwilldisableincomingrequests.This

shouldbethelastenablebittotogglewhenbringingthedeviceoutofresettobeginnormal

operation.

0Dataflowcontrolisdisabled.

1Dataflowcontrolisenabled.

1SOFTSoftstop.ThisbitandtheFREEbitdeterminehowtheSRIOperipheralbehavesduringemulation

halts.

0Hardstop.Allstatusregistersarefrozenindefaultstate.(ThismodeisnotsupportedontheSRIO

peripheral.)

1Softstop

0FREEFreerun

0TheSOFTbittakeseffect.

1Freerun.Peripheralignorestheemulationsuspendsignalandfunctionsnormally.

SerialRapidIO(SRIO) 112SPRUE13A–September2006

SubmitDocumentationFeedback