www.ti.com

5.29LSUInterruptConditionRoutingRegisters(LSU_ICRR0–LSU_ICRR3)

SRIORegisters

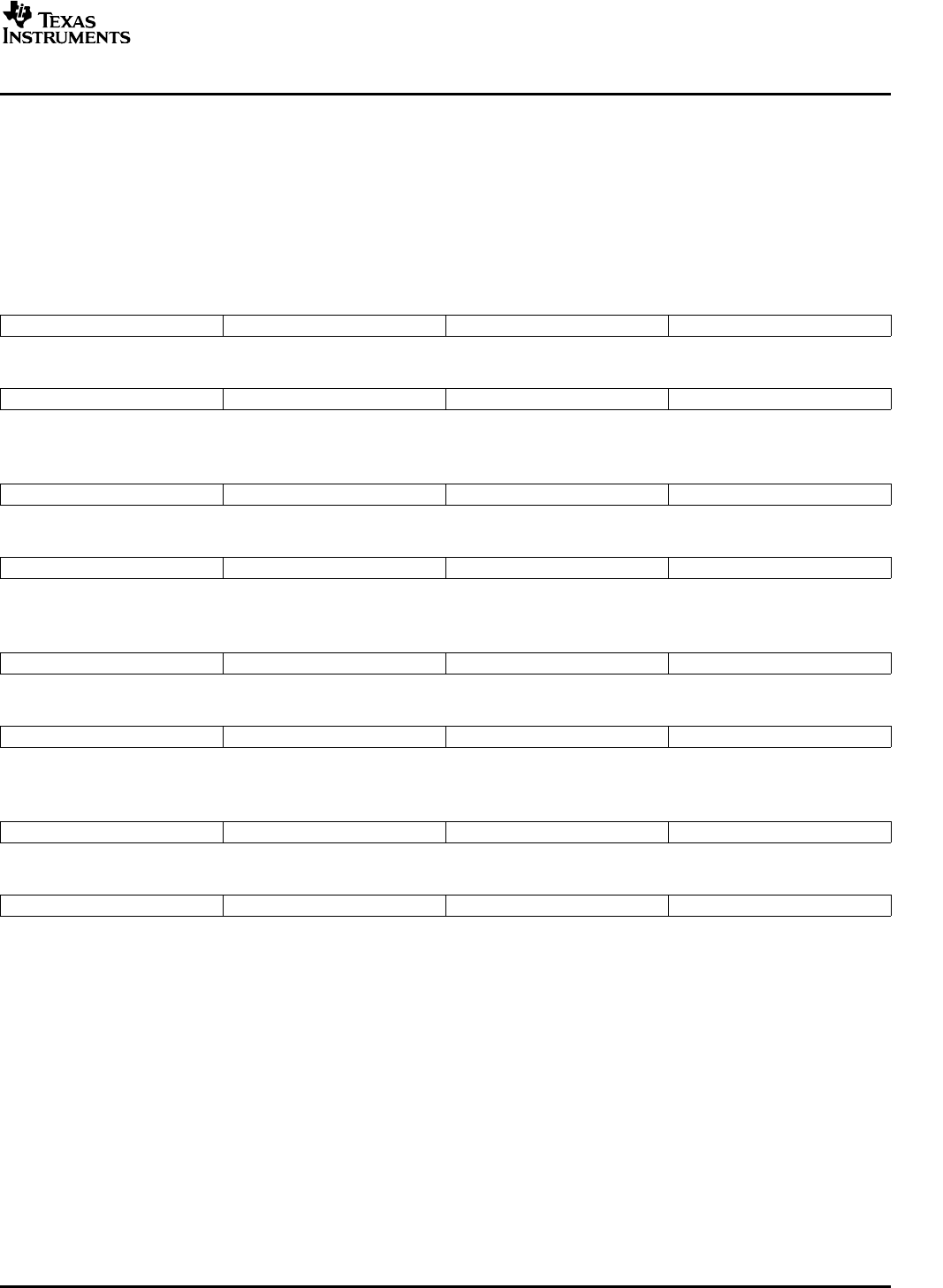

Figure90showstheICRRsfortheLSUinterruptrequests,andTable81showsthegeneraldescriptionfor

anICRxfieldinanyofthefourregisters.TheseregistersrouteLSUinterruptrequestsfromLSU_ICSRto

interruptdestinations.Forexample,ifICS4=1inLSU_ICSRandICR4=0000binLSU_ICRR0,LSU1

hasgeneratedatransaction-timeoutinterruptrequest,andthatrequestisroutedtointerruptdestination0.

ForadditionalprogrammingseeSection4.4.1.2.

Figure90.LSUInterruptConditionRoutingRegisters

LSUInterruptConditionRoutingRegister0(LSU_ICRR0)(AddressOffset02E0h)

3128272423201916

ICR7ICR6ICR5ICR4

R/W-0000R/W-0000R/W-0000R/W-0000

15121187430

ICR3ICR2ICR1ICR0

R/W-0000R/W-0000R/W-0000R/W-0000

LSUInterruptConditionRoutingRegister1(LSU_ICRR1)(AddressOffset02E4h)

3128272423201916

ICR15ICR14ICR13ICR12

R/W-0000R/W-0000R/W-0000R/W-0000

15121187430

ICR11ICR10ICR9ICR8

R/W-0000R/W-0000R/W-0000R/W-0000

LSUInterruptConditionRoutingRegister2(LSU_ICRR2)(AddressOffset02E8h)

3128272423201916

ICR23ICR22ICR21ICR20

R/W-0000R/W-0000R/W-0000R/W-0000

15121187430

ICR19ICR18ICR17ICR16

R/W-0000R/W-0000R/W-0000R/W-0000

LSUInterruptConditionRoutingRegister3(LSU_ICRR3)(AddressOffset02ECh)

3128272423201916

ICR31ICR30ICR29ICR28

R/W-0000R/W-0000R/W-0000R/W-0000

15121187430

ICR27ICR26ICR25ICR24

R/W-0000R/W-0000R/W-0000R/W-0000

LEGEND:R/W=Read/Write;-n=Valueafterreset

SPRUE13A–September2006SerialRapidIO(SRIO)147

SubmitDocumentationFeedback