www.ti.com

Source Address

DMA Read

Destination Address

Count

ByteCount

DSPAddress

RSV

InterruptReq

001723 8

DestID

25 24

IDSize

27 26

xambs

29 28

Priority

OutPortID

31 30

HopCount

Drbll

31 16 15

Packet

8 7 0

RapioIO Address/Config_offset

NodeID

CRC

16

Count*8

payload

2

xamsbs

1

wrptr

29

address

32

extaddr

8

srcTID

4

wrsize

4

trans

8

sourceID

8

destID

4

ftype

2

tt

2

prio

3

rsv

5

ackID

TXSharedBufferPool

rdsize/

wsize

rdptr/

wptr

Count

translator

LSU _REG4n

LSU _REG2n

LSU _REG3n

LSU _REG0

LSU _REG1

n

n

LSU _REG5n

2.3.3.1DetailedDataPathDescription

SRIOFunctionalDescription

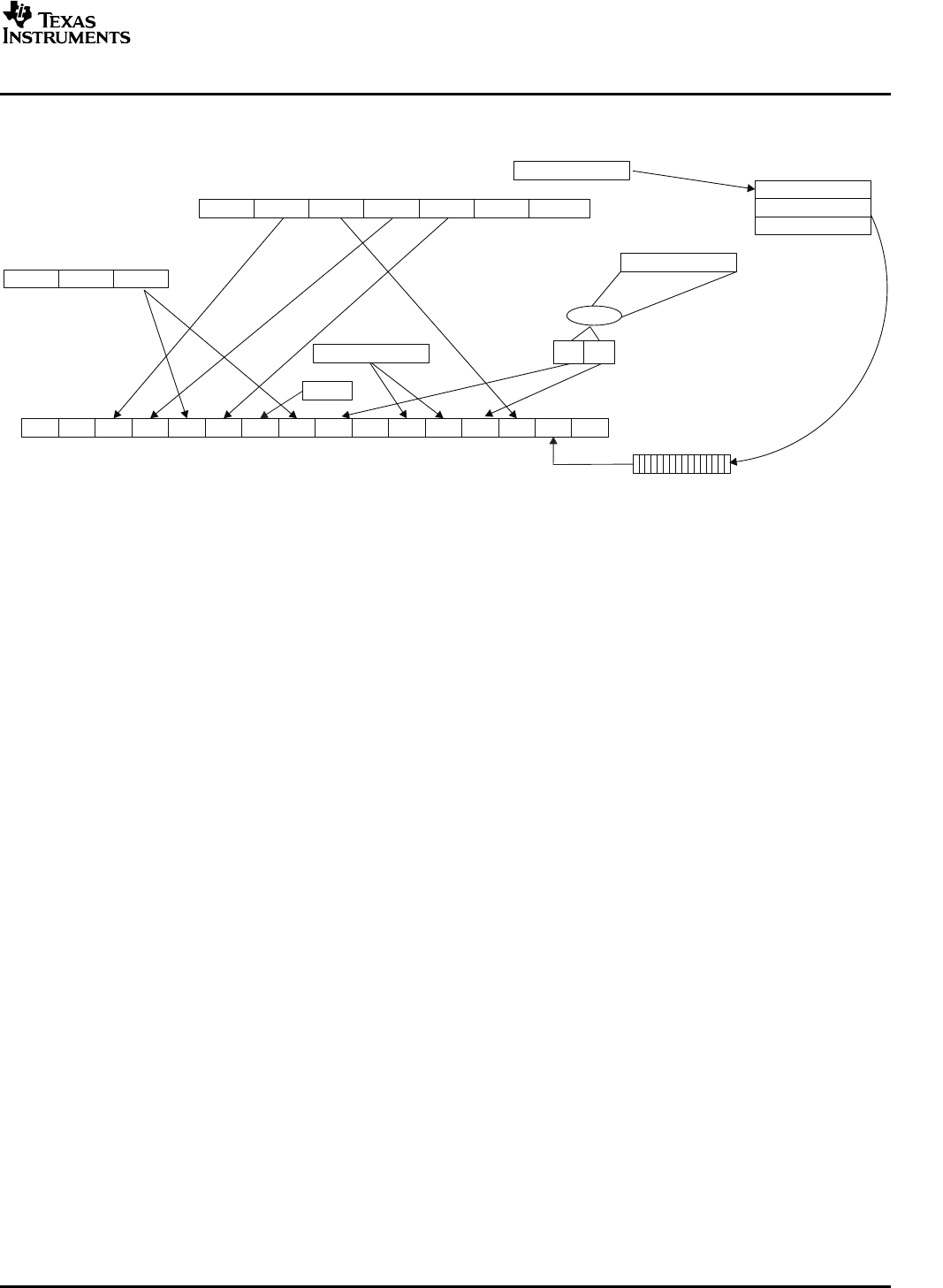

Figure14.ExampleBurstNWRITE_R

ForWRITEcommands,thepayloadiscombinedwiththeheaderinformationfromthecontrol/command

registersandbufferedinthesharedTXbufferresourcepool.Finally,itisforwardedtotheTXFIFOfor

transmission.READcommandshavenopayload.Inthiscase,onlythecontrol/commandregisterfields

arebufferedandusedtocreateaRapidIONREADpacket,whichisforwardedtotheTXFIFO.

CorrespondingresponsepacketpayloadsfromREADtransactionsarebufferedinthesharedRXbuffer

resourcepoolwhenforwardedfromthereceiveports.Bothpostedandnon-postedoperationsrelyonthe

OutPortIDcommandregisterfieldtospecifytheappropriateoutputport/FIFO.

ThedataisburstinternallytotheLoad/StoremoduleattheDMAclockrate.

TheLoad/StoremoduleisforgeneratingalloutgoingRapidIOdirectI/Opackets.Anyreadorwrite

transaction,otherthanthemessagingprotocol,usesthisinterface.Inaddition,outgoingDOORBELL

packetsaregeneratedthroughthisinterface.

ThedatapathforthismoduleusesDMAbusastheDMAinterface.Theconfigurationbusisusedbythe

CPUtoaccessthecontrol/commandregisters.Theregisterscontaintransferdescriptorsthatareneeded

toinitiateREADandWRITEpacketgeneration.Afterthetransferdescriptorsarewritten,flowcontrol

statusisqueried.TheunitexaminestheDESTIDandPRIORITYfieldsofLSUn_REG4todetermineifthat

flowhasbeenXoffd.Additionally,thefreebufferstatusoftheTXFIFOischecked(basedonthe

OutPortIDregisterfield).Onlyaftertheflowcontrolaccessisgranted,andaTXFIFObufferhasbeen

allocated,canaDMAbusreadcommandbeissuedforpayloaddatatobemovedintothesharedTX

buffer.DataismovedfromthesharedTXbuffertotheappropriateoutputTXFIFOinsimplesequential

orderbasedoncompletionoftheDMAbustransaction.However,iffabriccongestionoccurs,prioritycan

affecttheorderinwhichthedataleavestheTXFIFOs.

Hereareorderingmechanismexists,whichtransmitsthehighestprioritypacketsfirstifRETRY

acknowledges.OnceintheFIFO,thedataisguaranteedtobetransmittedthroughthepins.Alternatively,

ifanintendedflowhasbeenshutdown,theperipheralsignalstheCPUwithaninterrupttonotifythatthe

packetwasnotsentandsetsthecompletioncodeto010binthestatusregister.Theregistersareheld

untiltheinterruptserviceroutineiscompletebeforetheBSYsignalisreleased(BSY=0inLSUn_REG6)

andtheCPUcanthenrewriteoroverwritethetransferdescriptorswithnewdata.Figure15illustratesthe

datapathandbufferingthatisrequiredtosupporttheLoad/Storemodule.

SPRUE13A–September2006SerialRapidIO(SRIO)39

SubmitDocumentationFeedback