www.ti.com

5.48ReceiveCPPIControlRegister(RX_CPPI_CNTL)

SRIORegisters

EachbitinthisregisterindicateswhethertheassociatedRXbufferdescriptorqueuemustreceive

messagesintheorderthesourcedeviceattemptstotransmitthem.RX_CPPI_CNTLisshowninand

describedinTable116.Foradditionalprogramminginformation,seeSection2.3.4.1.

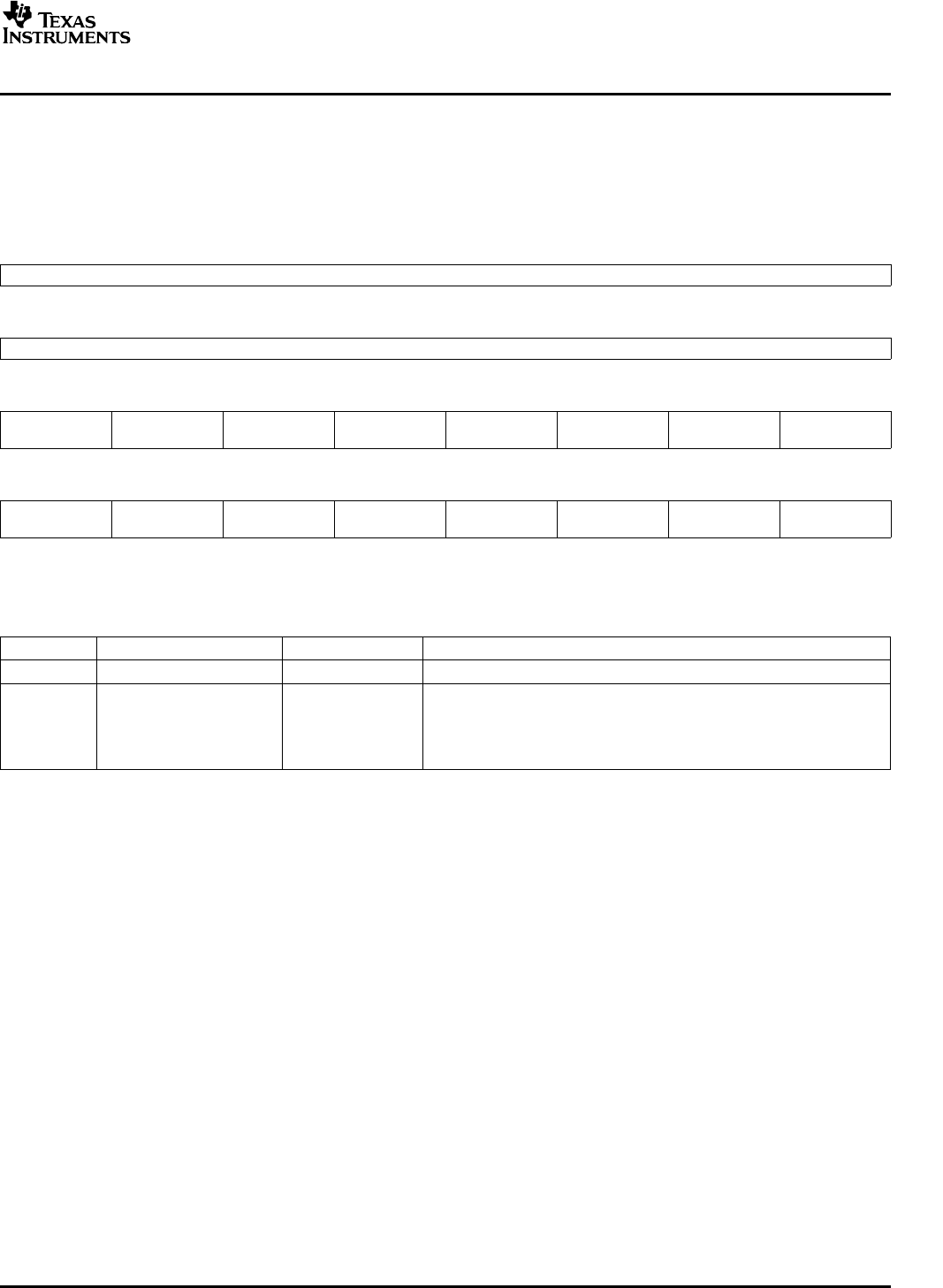

Figure111.ReceiveCPPIControlRegister(RX_CPPI_CNTL)(AddressOffset0744h)

3124

Reserved

R-00h

2316

Reserved

R-00h

15141312111098

QUEUE15_QUEUE14_QUEUE13_QUEUE12_QUEUE11_QUEUE10_QUEUE9_QUEUE8_

IN_ORDERIN_ORDERIN_ORDERIN_ORDERIN_ORDERIN_ORDERIN_ORDERIN_ORDER

R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0

76543210

QUEUE7_QUEUE6_QUEUE5_QUEUE4_QUEUE3_QUEUE2_QUEUE1_QUEUE0_

IN_ORDERIN_ORDERIN_ORDERIN_ORDERIN_ORDERIN_ORDERIN_ORDERIN_ORDER

R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=Valueafterreset

Table116.ReceiveCPPIControlRegister(RX_CPPI_CNTL)FieldDescriptions

BitFieldValueDescription

31–16Reserved0000hReserved

15–0QUEUEn_IN_ORDERQueueninorder

(n=15to0)

0Allowsout-of-ordermessagereception

1Requiresin-ordermessagereception.Usedforapplicationswith

dedicatedsource-destinationflows.

SPRUE13A–September2006SerialRapidIO(SRIO)173

SubmitDocumentationFeedback