www.ti.com

InterruptConditions

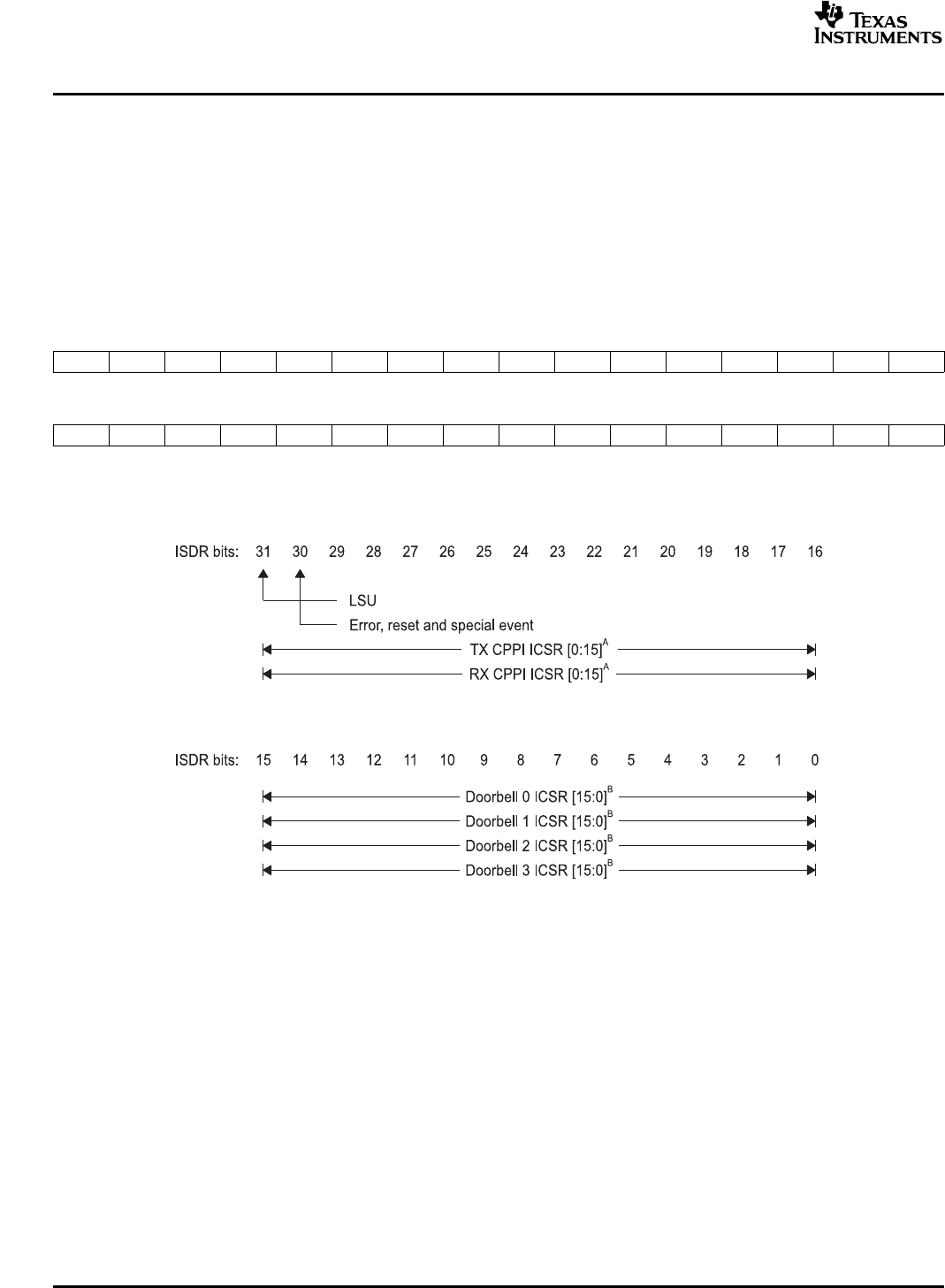

eachbitintheISDR.BitswithintheLSUinterruptconditionstatusregister(ICSR)arelogicallygroupedfor

agivencoreandORedtogetherintoasinglebit(bit31)ofthedecoderegister.Similarly,thebitswithin

theError,Reset,andSpecialEventICSRareORedtogetherintobit30ofthedecoderegister.TheTX

CPPIandRXCPPIinterruptsources(oneforeachbufferdescriptorqueue)canbemappedtobits31–16

asshowninFigure60.Thedoorbellinterruptsourcescanbemappedtobits15–0.

AninterruptsourceismappedtoISDRbitsonlyiftheICRRforthatinterruptsourceroutesittothe

correspondinginterruptdestination.Whenmultipleinterruptsourcesaremappedtothesamebit,thebit

statusisalogicalORofthoseinterruptsources.Themappingofinterruptsourcebitstodecodebitsis

fixedandisnotprogrammable.

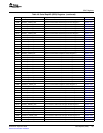

Figure59.InterruptStatusDecodeRegister(INTDSTn_DECODE)

31302928272625242322212019181716

ISD31ISD30ISD29ISD28ISD27ISD26ISD25ISD24ISD23ISD22ISD21ISD20ISD19ISD18ISD17ISD16

R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0

1514131211109876543210

ISD15ISD14ISD13ISD12ISD11ISD10ISD9ISD8ISD7ISD6ISD5ISD4ISD3ISD2ISD1ISD0

R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0R-0

LEGEND:R=Readonly;-n=Valueafterreset

Figure60.InterruptSourcesAssignedtoISDRBits

APleasenotethatbits0through15ofthisICSRcorrespondtobits31through16oftheISDR.Forexample,bit15of

theICSRcorrespondstobit31oftheISDR,andsoon.

BPleasenotethatbits15through0ofthisICSRcorrespondtobits15through0oftheISDR.Forexample,bit15of

theICSRcorrespondstobit15oftheISDR,andsoon.

AsanexampleofreadinganISDR,ifbit29oftheISDRisset,thisindicatesthatthereisapending

interruptoneithertheTXCPPIqueue2orRXCPPIqueue2.Figure61illustratesthedecoderoutingfor

thisexample.

98SerialRapidIO(SRIO)SPRUE13A–September2006

SubmitDocumentationFeedback