www.ti.com

5.15SERDESMacroConfigurationRegistern(SERDES_CFGn_CNTL)

SRIORegisters

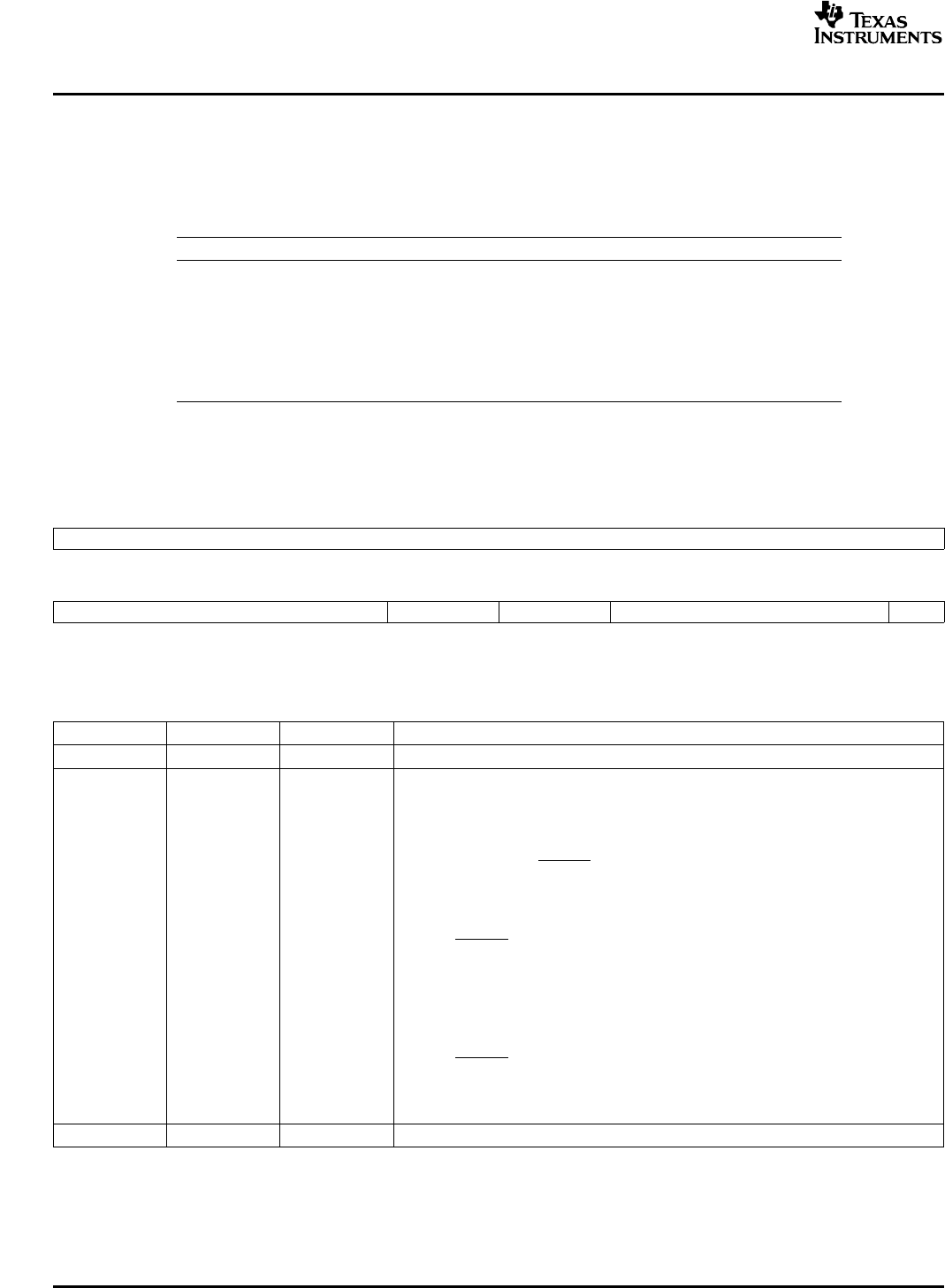

Therearefouroftheseregisters,tosupportfourports(seeTable63).ThegeneralformforaSERDES

transmitchannelconfigurationregisterissummarizedbyFigure76andTable64.SeeSection2.3.2.1for

acompleteexplanationoftheprogrammingofthisregister.

Table63.SERDES_CFGn_CNTLRegistersandtheAssociatedPorts

RegisterAddressOffsetAssociatedPort

SERDES_CFG0_CNTL0120hPort0,Port1,Port2,andPort3

SERDES_CFG1_CNTL0124hNotUsed.Programas

0x00000000

SERDES_CFG2_CNTL0128hNotUsed.Programas

0x00000000

SERDES_CFG3_CNTL012ChNotUsed.Programas

0x00000000

Figure76.SERDESMacroConfigurationRegistern(SERDES_CFGn_CNTL)

3116

Reserved

R-0

15109876510

ReservedLBReservedMPYENPLL

R-0R/W-0R-0R/W-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;-n=Valueafterreset

Table64.SERDESMacroConfigurationRegistern(SERDES_CFGn_CNTL)FieldDescriptions

BitFieldValueDescription

31–10Reserved0Reserved

9–8LBLoopbandwidth.Specifyloopbandwidthsettings.Jitteronthereferenceclockwill

degradeboththetransmiteyeandreceiverjittertolerancetherebyimpairingsystem

performance.PerformanceoftheintegratedPLLcanbeoptimizedaccordingtothe

jittercharacteristicsofthereferenceclockviatheLBfield.

00bFrequencydependentbandwidth.ThePLLbandwidthissettoatwelfthofthe

frequencyofRIOCLK/RIOCLK.Thissettingissuitableformostsystemsthatinputthe

referenceclockviaalowjitterinputcell,andisrequiredforstandardscompliance

01bReserved

10bLowbandwidth.ThePLLbandwidthissettoatwentiethofthefrequencyof

RIOCLK/RIOCLK,or3MHz(whicheverislarger).Insystemswherethereference

clockisdirectlyinputviaalowjitterinputcell,butisoflowerquality,thissettingmay

offerbetterperformance.Itwillreducetheamountofreferenceclockjittertransferred

throughthePLL.However,italsoincreasesthesusceptibilitytoloopnoisegenerated

withinthePLLitself.Itisdifficulttopredictwhethertheimprovementintheformerwill

morethanoffsetthedegradationinthelatter.

11bHighbandwidth.ThePLLbandwidthissettoaeighthofthefrequencyof

RIOCLK/RIOCLK.Thisisthesettingappropriateforsystemswherethereference

clockiscleanedthroughanultralowjitterLC-basedPLL.Standardscompliancewill

beachievedevenifthereferenceclockinputtothecleanerPLLisoutsidethe

specificationforthestandard.

7–6Reserved0Reserved

130SerialRapidIO(SRIO)SPRUE13A–September2006

SubmitDocumentationFeedback