www.ti.com

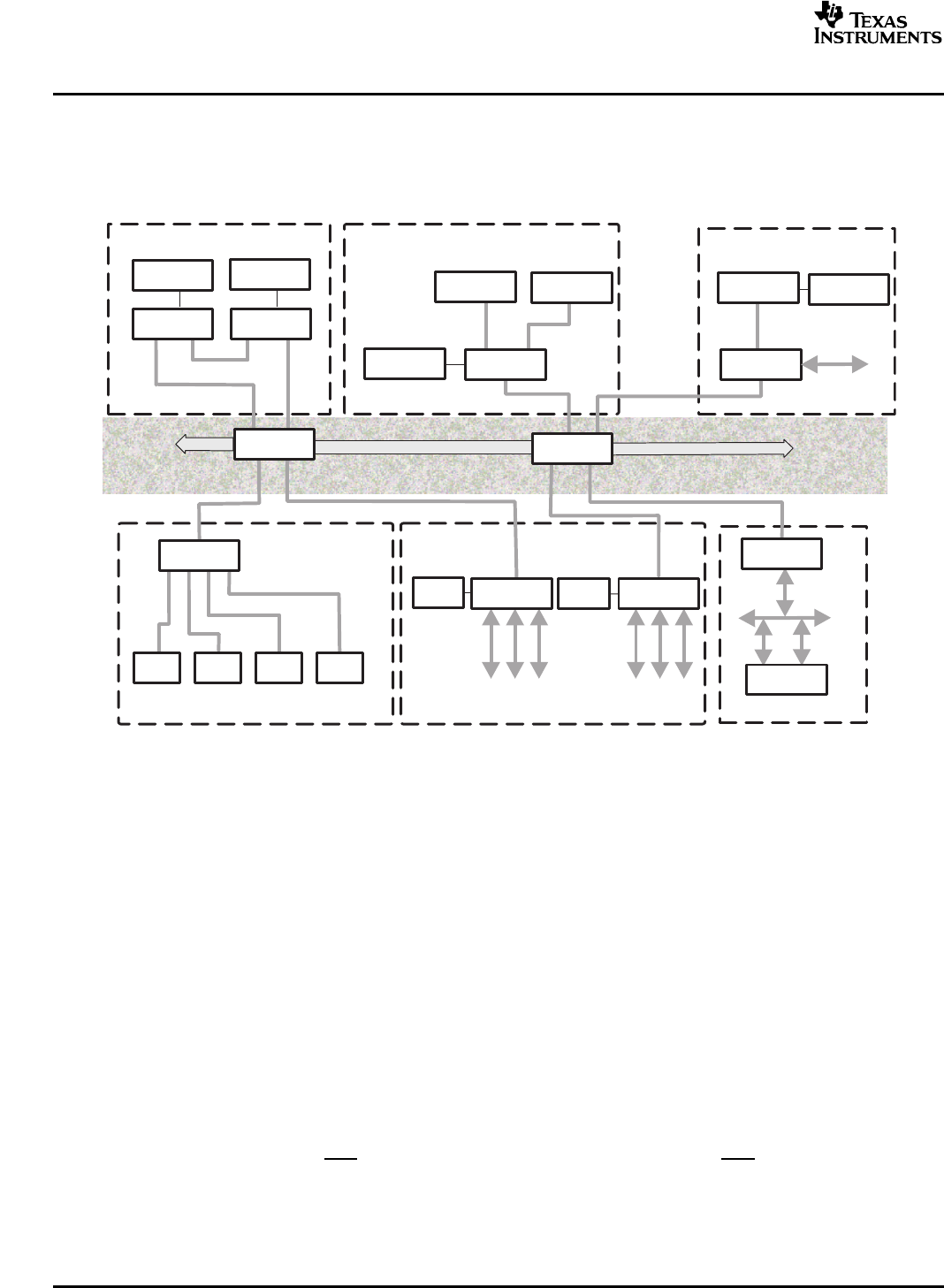

1.1.2RapidIOInterconnectArchitecture

HostSubsystem

I/OControlSubsystem

DSP Farm

TDM,GMII,Utopia

CommunicationsSubsystem PCISubsystem

InfiniBand HCA™

ToSystem Area

Network

Memory

Memory

Memory

Memory

RapidIO

RapidIO RapidIO

RapidIO

RapidIO

Backplane

PCI

RapidIO

RapidIO

RapidIO

RapidIO

Switch

Control

Processor

IO

Processor

RapidIOto

InfiniBand

RapidIO

Switch

RapidIO

Switch

Legacy

Comm

Processor

RapidIO

Switch

RapidIOto

PCIBridge

ASIC/FPGA

Memory

Memory

Host

Processor

Host

Processor

DSP DSP DSP DSP

Comm

Processor

1.1.3PhysicalLayer1x/4xLP-SerialSpecification

Overview

Theinterconnectarchitectureisdefinedasapacketswitchedprotocolindependentofaphysicallayer

implementation.Figure2illustratestheinterconnectionsystem.

Figure2.RapidIOInterconnectArchitecture

(1)InfiniBand™isatrademarkoftheInfiniBandTradeAssociation.

Currently,therearetwophysicallayerspecificationsrecognizedbytheRapidIOTradeAssociation:8/16

LP-LVDSand1x/4xLP-Serial.The8/16LP-LVDSspecificationisapoint-to-pointsynchronousclock

sourcingDDRinterface.The1x/4xLP-Serialspecificationisapoint-to-point,ACcoupled,clockrecovery

interface.Thetwophysicallayerspecificationsarenotcompatible.

SRIOcomplieswiththe1x/4xLP-Serialspecification.Theserializer/deserializer(SERDES)technologyin

SRIOalsoalignswiththatspecification.

TheRapidIOPhysicalLayer1x/4xLP-SerialSpecificationcurrentlycoversthreefrequencypoints:1.25,

2.5,and3.125Gbps.ThisdefinesthetotalbandwidthofeachdifferentialpairofI/Osignals.An8-bit/10-bit

encodingschemeensuresampledatatransitionsfortheclockrecoverycircuits.Duetothe8-bit/10-bit

encodingoverhead,theeffectivedatabandwidthperdifferentialpairis1.0,2.0,and2.5Gbps

respectively.SerialRapidIOonlyspecifiestheseratesforboththe1xand4xports.A1xportisdefinedas

1TXand1RXdifferentialpair.A4xportisacombinationoffourofthesepairs.Thisdocumentdescribes

a4xRapidIOportthatcanalsobeconfiguredasfour1xports,thusprovidingascalableinterfacecapable

ofsupportingadatabandwidthof1to10Gbps.

Figure3showshowtointerfacetwo1xdevicesandtwo4xdevices.Eachpositivetransmitdataline(TDx)

ononedeviceisconnectedtoapositivereceivedataline(RDx)ontheotherdevice.Likewise,each

negativetransmitdataline(TDx)isconnectedtoanegativereceivedataline(RDx).

18SerialRapidIO(SRIO)SPRUE13A–September2006

SubmitDocumentationFeedback