www.ti.com

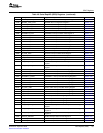

4.5InterruptStatusDecodeRegisters

InterruptConditions

Figure58.Error,Reset,andSpecialEventInterruptConditionRoutingRegisters

Error,Reset,andSpecialEventICRR(ERR_RST_EVNT_ICRR)(AddressOffset02F0h)

31

Reserved

R-0

121187430

ReservedICR2ICR1ICR0

R-0R/W-0000R/W-0000R/W-0000

Error,Reset,&SpecialEventICRR2(ERR_RST_EVNT_ICRR2)(AddressOffset02F4h)

3116

Reserved

R-0

15121187430

ICR11ICR10ICR9ICR8

R/W-0000R/W-0000R/W-0000R/W-0000

Error,Reset,andSpecialEventICRR3(ERR_RST_EVNT_ICRR3)(AddressOffset02F8h)

31

Reserved

R-0

430

ReservedICR16

R-0R/W-0000

LEGEND:R/W=Read/Write;R=Readonly;-n=Valueafterreset

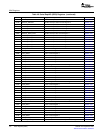

Thereare8blocksoftheICSRstoindicatethesourceofapendinginterrupt.

0x0200:Doorbell0interrupts

0x0210:Doorbell1interrupts

0x0220:Doorbell2interrupts

0x0230:Doorbell3interrupts

0x0240:RXCPPIinterrupts

0x0250:TXCPPIinterrupts

0x0260:LSUinterrupts

0x0270:Error,Reset,andSpecialEventinterrupts

Toreducethenumberofreads(upto5reads)requiredtofindthesourcebit,anInterruptStatusDecode

Register(ISDR)isimplementedforeachsupportedphysicalinterruptdestination.Thedevicesupportsup

toeightinterruptdestinations,INTDST0–INTDST7.ThenamesoftheISDRsandtheiraddressoffsetsare:

•INTDST0_DECODE(Addressoffset0300h)

•INTDST1_DECODE(Addressoffset0304h)

•INTDST2_DECODE(Addressoffset0308h)

•INTDST3_DECODE(Addressoffset030Ch)

•INTDST4_DECODE(Addressoffset0310h)

•INTDST5_DECODE(Addressoffset0314h)

•INTDST6_DECODE(Addressoffset0318h)

•INTDST7_DECODE(Addressoffset031Ch)

Asidefromsupportingdifferentinterruptdestinations,theISDRsarethesameincontentandfunctionality.

TheregisterfieldsareshowninFigure59.Figure60showswhichinterruptsourcescanbemappedto

SPRUE13A–September2006SerialRapidIO(SRIO)97

SubmitDocumentationFeedback