www.ti.com

2.3.9Endianness

SRIOFunctionalDescription

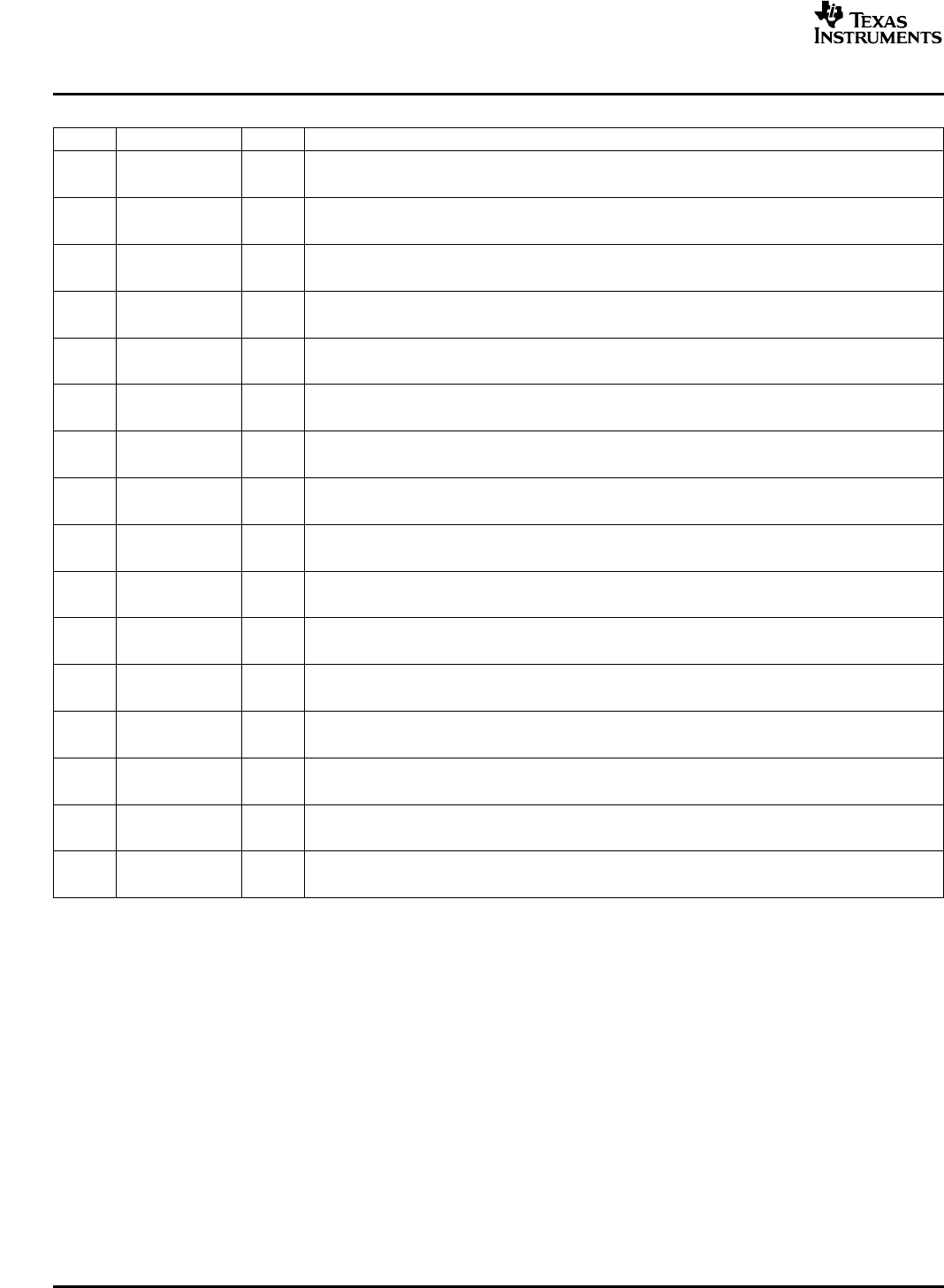

Table25.FieldsWithinEachFlowMask

BitFieldValueDescription

15FL150TXsourcedoesnotsupportFlow15fromtableentry

1TXsourcesupportsFlow15fromtableentry

14FL140TXsourcedoesnotsupportFlow14fromtableentry

1TXsourcesupportsFlow14fromtableentry

13FL130TXsourcedoesnotsupportFlow13fromtableentry

1TXsourcesupportsFlow13fromtableentry

12FL120TXsourcedoesnotsupportFlow12fromtableentry

1TXsourcesupportsFlow12fromtableentry

11FL110TXsourcedoesnotsupportFlow11fromtableentry

1TXsourcesupportsFlow11fromtableentry

10FL100TXsourcedoesnotsupportFlow10fromtableentry

1TXsourcesupportsFlow10fromtableentry

9FL90TXsourcedoesnotsupportFlow9fromtableentry

1TXsourcesupportsFlow9fromtableentry

8FL80TXsourcedoesnotsupportFlow8fromtableentry

1TXsourcesupportsFlow8fromtableentry

7FL70TXsourcedoesnotsupportFlow7fromtableentry

1TXsourcesupportsFlow7fromtableentry

6FL60TXsourcedoesnotsupportFlow6fromtableentry

1TXsourcesupportsFlow6fromtableentry

5FL50TXsourcedoesnotsupportFlow5fromtableentry

1TXsourcesupportsFlow5fromtableentry

4FL40TXsourcedoesnotsupportFlow4fromtableentry

1TXsourcesupportsFlow4fromtableentry

3FL30TXsourcedoesnotsupportFlow3fromtableentry

1TXsourcesupportsFlow3fromtableentry

2FL20TXsourcedoesnotsupportFlow2fromtableentry

1TXsourcesupportsFlow2fromtableentry

1FL10TXsourcedoesnotsupportFlow1fromtableentry

1TXsourcesupportsFlow1fromtableentry

0FL00TXsourcedoesnotsupportFlow0fromtableentry

1TXsourcesupportsFlow0fromtableentry

RapidIOisbasedonBigEndian.ThisisdiscussedindetailinSection2.4oftheRapidIOInterconnect

Specification.Essentially,BigEndianspecifiestheaddressorderingasthemostsignificantbit/bytefirst.

Forexample,inthe29-bitaddressfieldofaRapidIOpacket(showninFigure6)theleft-mostbitthatis

transmittedfirstintheserialbitstreamistheMSBoftheaddress.Likewise,thedatapayloadofthepacket

isdouble-wordalignedBigEndian,whichmeanstheMSBistransmittedfirst.Bit0ofallthe

RapidIO-definedMMRregistersistheMSB.

AllEndian-specificconversionishandledwithintheperipheral.Fordouble-wordalignedpayloads,the

datashouldbewrittencontiguouslyintomemorybeginningatthespecifiedaddress.Anyunaligned

payloadswillbepaddedandproperlyalignedwithinthe8-byteboundary.Inthiscase,WDPTR,RDSIZE,

andWRSIZERapidIOheaderfieldsindicatethebytepositionofthedatawithinthedouble-word

boundary.AnexampleofanunalignedtransferisshowninSection2.4oftheRapidIOInterconnect

Specification.

68SerialRapidIO(SRIO)SPRUE13A–September2006

SubmitDocumentationFeedback