System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-17

ID013010 Non-Confidential, Unrestricted Access

To access the TCM Type Register, read CP15 with:

MRC p15, 0, <Rd>, c0, c0, 2 ; Returns TCM type register

Note

• The ATCM and BTCM fields in the TCM Type Register occupy the same space as the

ITCM and DTCM fields as defined by the ARM Architecture. These fields, and the

corresponding TCM interfaces, can be considered equivalent to those defined in the

Architecture.

• The ARM Architecture requires only the ITCM to be accessible from both instruction and

data sides. In the Cortex-R4 processor, both ATCM and BTCM are accessible from both

instruction and data sides.

4.2.5 c0, MPU Type Register

The MPU Type Register holds the value for the number of instruction and data memory regions

implemented in the processor.

The MPU Type Register is:

• read-only register

• accessible in Privileged mode only.

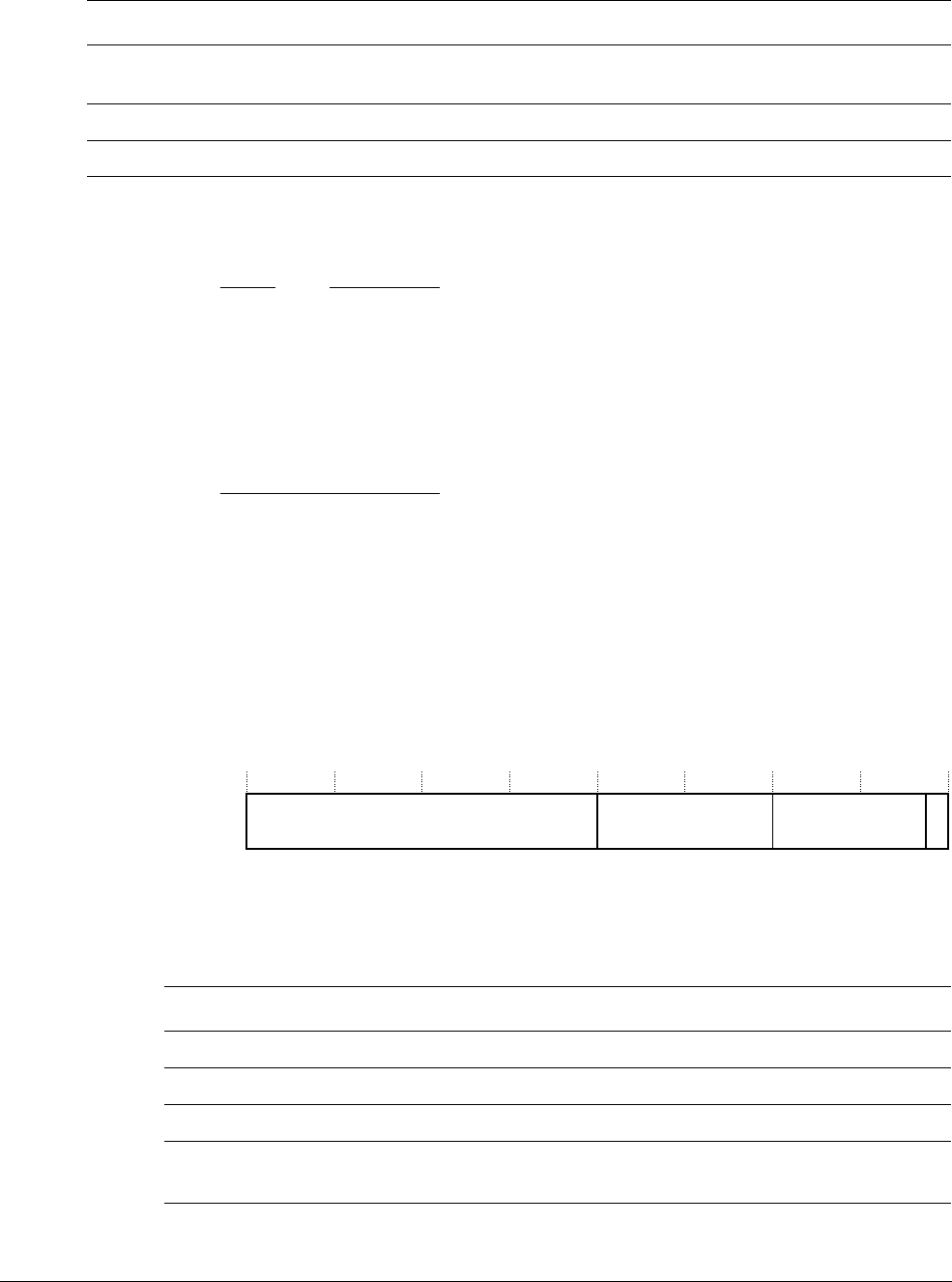

Figure 4-10 shows the arrangement of bits in the register.

Figure 4-10 MPU Type Register format

Table 4-6 shows how the bit values correspond with the MPU Type Register functions.

To access the MPU Type Register, read CP15 with:

[18:16] BTCM Specifies the number of BTCMs implemented. This is always set to

b001

because the processor

has one BTCM.

[15:3] Reserved SBZ.

[2:0] ATCM Specifies the number of ATCMs implemented. Always set to b001. The processor has one ATCM.

Table 4-5 TCM Type Register bit functions (continued)

Bits Field Function

SReserved

31 16 8 7 1 0

ReservedDRegion

Table 4-6 MPU Type Register bit functions

Bits Field Function

[31:16] Reserved SBZ.

[15:8] DRegion Specifies the number of unified MPU regions. Set to 0, 8 or 12 data MPU regions.

[7:1] Reserved SBZ.

[0] S Specifies the type of MPU regions, unified or separate, in the processor.

Always set to 0, the processor has unified memory regions.