AC Characteristics

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 15-6

ID013010 Non-Confidential, Unrestricted Access

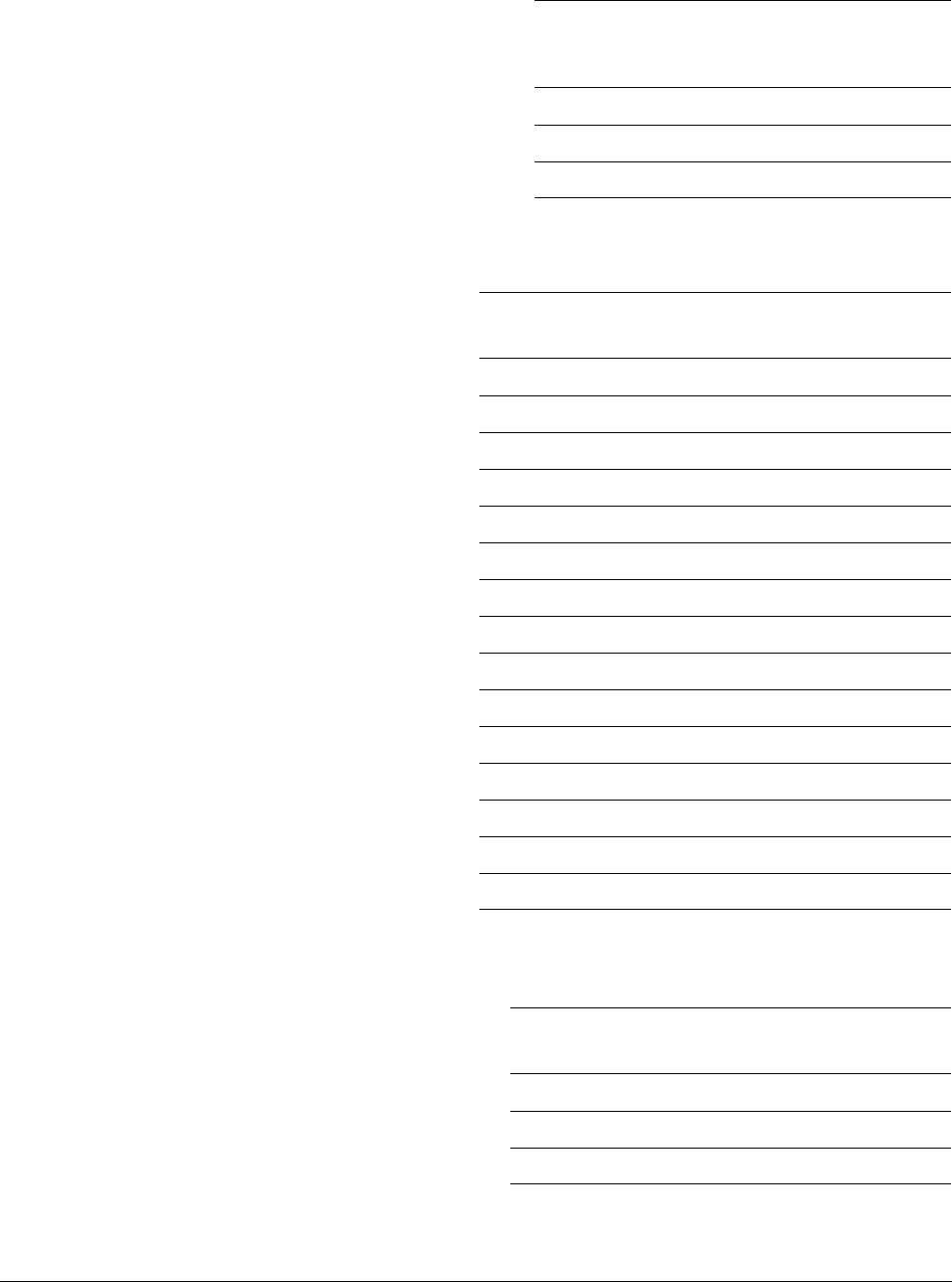

Table 15-6 shows the input timing parameters for the debug input ports.

Table 15-7 shows the input timing parameters for the ETM input ports.

Clock uncertainty 60% AWPA R ITY S

Clock uncertainty 60% WPARITYS

Clock uncertainty 60% ARPARITYS

Table 15-6 Debug input ports timing parameters

Input delay

minimum

Input delay

maximum

Signal name

Clock uncertainty 50% DBGEN

Clock uncertainty 50% NIDEN

Clock uncertainty 50% EDBGRQ

Clock uncertainty 50% PCLKENDBG

Clock uncertainty 50% PSELDBG

Clock uncertainty 50% PADDRDBG[11:2]

Clock uncertainty 50% PADDRDBG31

Clock uncertainty 50% PWDATADBG[31:0]

Clock uncertainty 50% PENABLEDBG

Clock uncertainty 50% PWRITEDBG

Clock uncertainty 10% DBGROMADDR[31:12]

Clock uncertainty 10% DBGROMADDRV

Clock uncertainty 10% DBGSELFADDR[31:12]

Clock uncertainty 10% DBGSELFADDRV

Clock uncertainty 50% DBGRESTART

Table 15-7 ETM input ports timing parameters

Input delay

minimum

Input delay

maximum

Signal name

Clock uncertainty 50% ETMPWRUP

Clock uncertainty 50% nETMWFIREADY

Clock uncertainty 50% ETMEXTOUT[1:0]

Table 15-5 AXI slave input port timing parameters (continued)

Input delay

minimum

Input

delay

maximum

Signal name