Debug

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 11-14

ID013010 Non-Confidential, Unrestricted Access

11.4.5 CP14 c1, Debug Status and Control Register

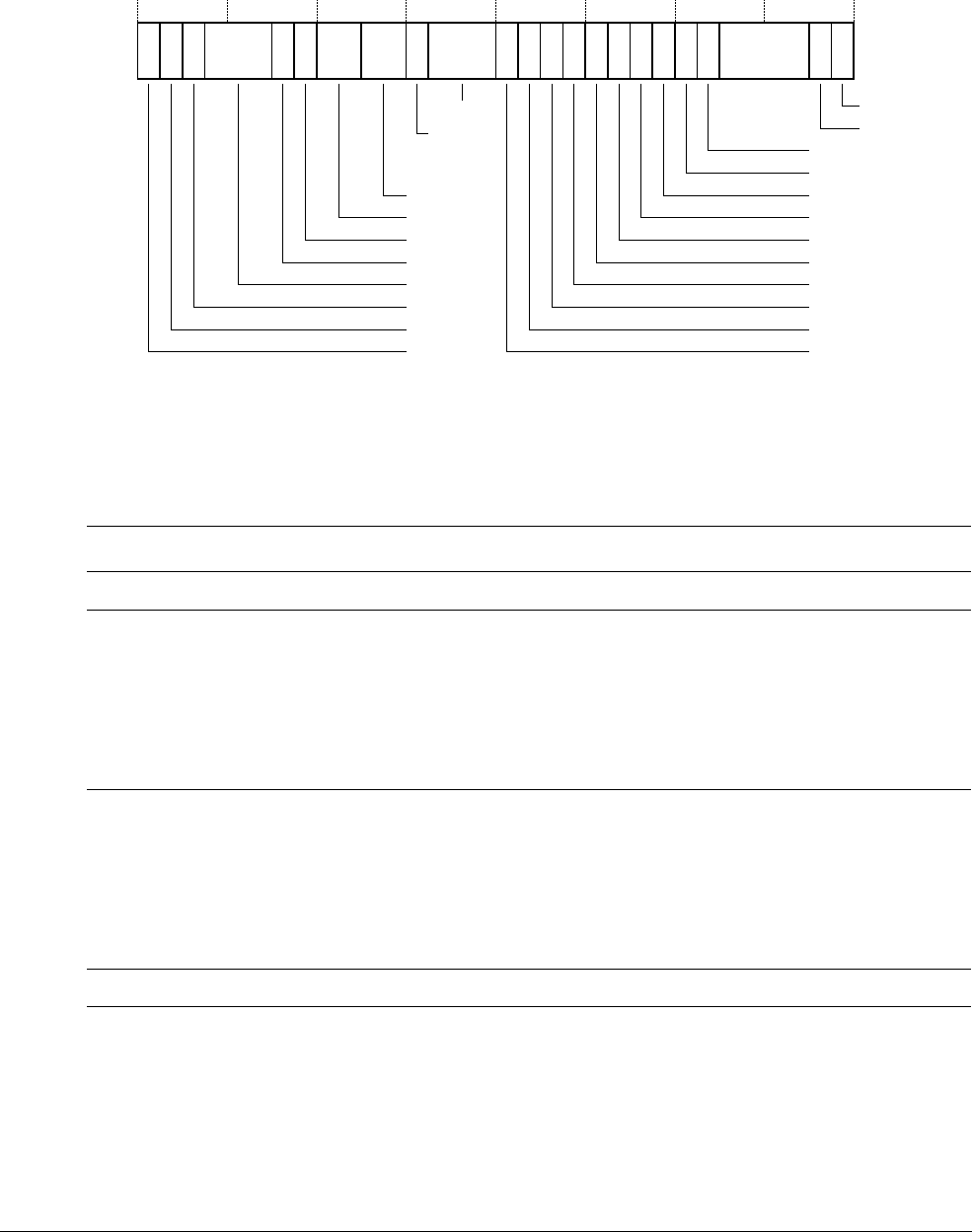

The DSCR contains status and control information about the debug unit. Figure 11-5 shows the

bit arrangement of the DSCR.

Figure 11-5 Debug Status and Control Register format

Table 11-10 shows how the bit values correspond with Debug Status and Control Register

functions.

31 30 29 28

16 15 14 13 12 11 10 6 5 2 1 0

MOE

978

Core halted

Core restarted

26 25 24 23

PipeAdv

InstrCompl

22 21 20 19 18

Monitor mode

Halting mode

ARM

DbgAck

IntDis

Comms

Sticky imprecise abort

Sticky Undefined

Reserved

Sticky precise abort

DTR access

Discard

imprecise

abort

27

Reserved

DTRTXfull

DTRRXfull

Reserved

Reserved

Reserved

Table 11-10 Debug Status and Control Register functions

Bits Field Function

[31] Reserved RAZ on reads, SBZP on writes.

[30] DTRRXfull The DTRRXfull flag:

0 = Read-DTR, DTRRX, empty, reset value

1 = Read-DTR, DTRRX, full.

When set, this flag indicates to the processor that there is data available to read at the

DTRRX. It is automatically set on writes to the DTRRX by the debugger, and is cleared

when the processor reads the CP14 DTR. If the flag is not set, the DTRRX returns an

Unpredictable value.

[29] DTRTXfull The DTRTXfull flag:

0 = Write-DTR, DTRTX, empty, reset value

1 = Write-DTR, DTRTX, full.

When clear, this flag indicates to the processor that the DTRTX is ready to receive data. It

is automatically cleared on reads of the DTRTX by the debugger, and is set when the

processor writes to the CP14 DTR. If this bit is set and the processor attempts to write to

the DTRTX, the register contents are overwritten and the DTRRXfull flag remains set.

[28:26] Reserved RAZ on reads, SBZP on writes.

[25] PipeAdv Sticky pipeline advance read-only bit. This bit enables the debugger to detect whether the

processor is idle. In some situations, this might mean that the system bus port is

deadlocked. This bit is set to 1 when the processor pipeline retires one instruction. It is

cleared by a write to DRCR[3].

0 = no instruction has completed execution since the last time this bit was cleared

1 = an instruction has completed execution since the last time this bit was cleared.