Level One Memory System

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 8-28

ID013010 Non-Confidential, Unrestricted Access

• Write a line to the eviction buffer in one cycle, a 256-bit read access.

• Fill a line in one cycle from the linefill buffer, a 256-bit write access.

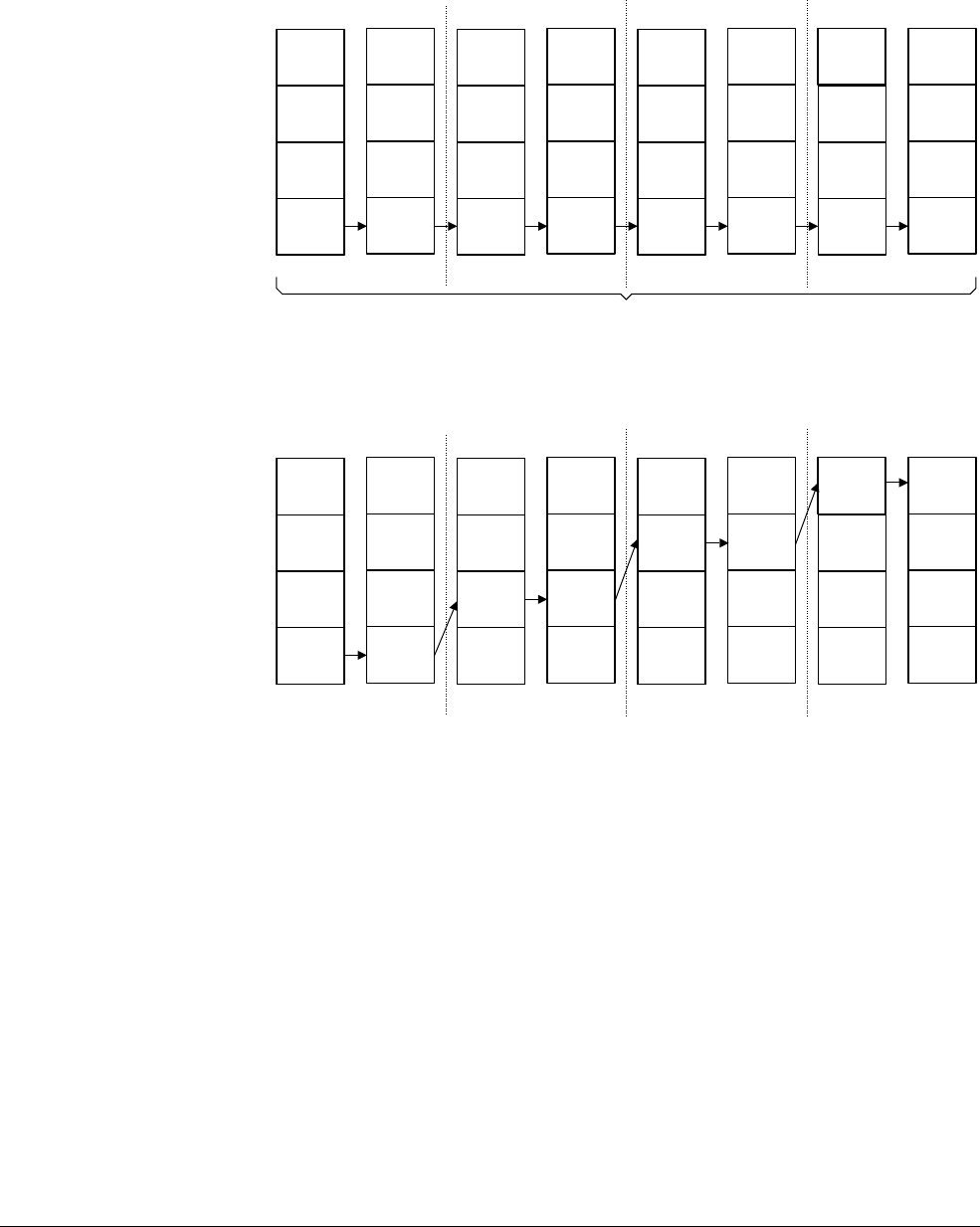

Figure 8-3 shows a cache look-up being performed on all banks with one RAM access.

Figure 8-3 Nonsequential read operation performed with one RAM access.

Figure 8-4 shows the appropriate bank RAM being selected for a sequential read operation.

Figure 8-4 Sequential read operation performed with one RAM access

The data RAM organization is optimized for 64-bit read operations, because with the same

address, two words on the same way can be selected.

Data RAM sizes depend on the build option selected, and are described in:

• Data RAM sizes without parity or ECC implemented on page 8-29

• Data RAM sizes with parity implemented on page 8-29

• Data RAM sizes with ECC implemented on page 8-30.

RAM address

0

1

2

3

Way 1

Word 6

Bank 0

Way 1

Word 7

Way 2

Word 4

Way 2

Word 5

Way 3

Word 2

Way 3

Word 3

Way 0

Word 0

Way 0

Word 1

Bank 1

Way 2

Word 6

Bank 2

Way 2

Word 7

Way 3

Word 4

Way 3

Word 5

Way 0

Word 2

Way 0

Word 3

Way 1

Word 0

Way 1

Word 1

Bank 3

Way 3

Word 6

Bank 4

Way 3

Word 7

Way 0

Word 4

Way 0

Word 5

Way 1

Word 2

Way 1

Word 3

Way 2

Word 0

Way 2

Word 1

Bank 5

Way 0

Word 7

Way 1

Word 4

Way 1

Word 5

Way 2

Word 2

Way 2

Word 3

Way 3

Word 0

Way 3

Word 1

Bank 7

Bank 6

Way 0

Word 6

256-bit wide

RAM address

0

1

2

3

Way 1

Word 6

Bank 0

Way 1

Word 7

Way 2

Word 4

Way 2

Word 5

Way 3

Word 2

Way 3

Word 3

Way 0

Word 0

Way 0

Word 1

Bank 1

Way 2

Word 6

Bank 2

Way 2

Word 7

Way 3

Word 4

Way 3

Word 5

Way 0

Word 2

Way 0

Word 3

Way 1

Word 0

Way 1

Word 1

Bank 3

Way 3

Word 6

Bank 4

Way 3

Word 7

Way 0

Word 4

Way 0

Word 5

Way 1

Word 2

Way 1

Word 3

Way 2

Word 0

Way 2

Word 1

Bank 5

Way 0

Word 7

Way 1

Word 4

Way 1

Word 5

Way 2

Word 2

Way 2

Word 3

Way 3

Word 0

Way 3

Word 1

Bank 7

Bank 6

Way 0

Word 6