System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-30

ID013010 Non-Confidential, Unrestricted Access

c0, Instruction Set Attributes Register 3, ISAR3

The Instruction Set Attributes Register 3 provides information about the instruction set that the

processor supports beyond the basic set.

The Instruction Set Attributes Register 3 is:

• a read-only registers

• accessible in Privileged mode only.

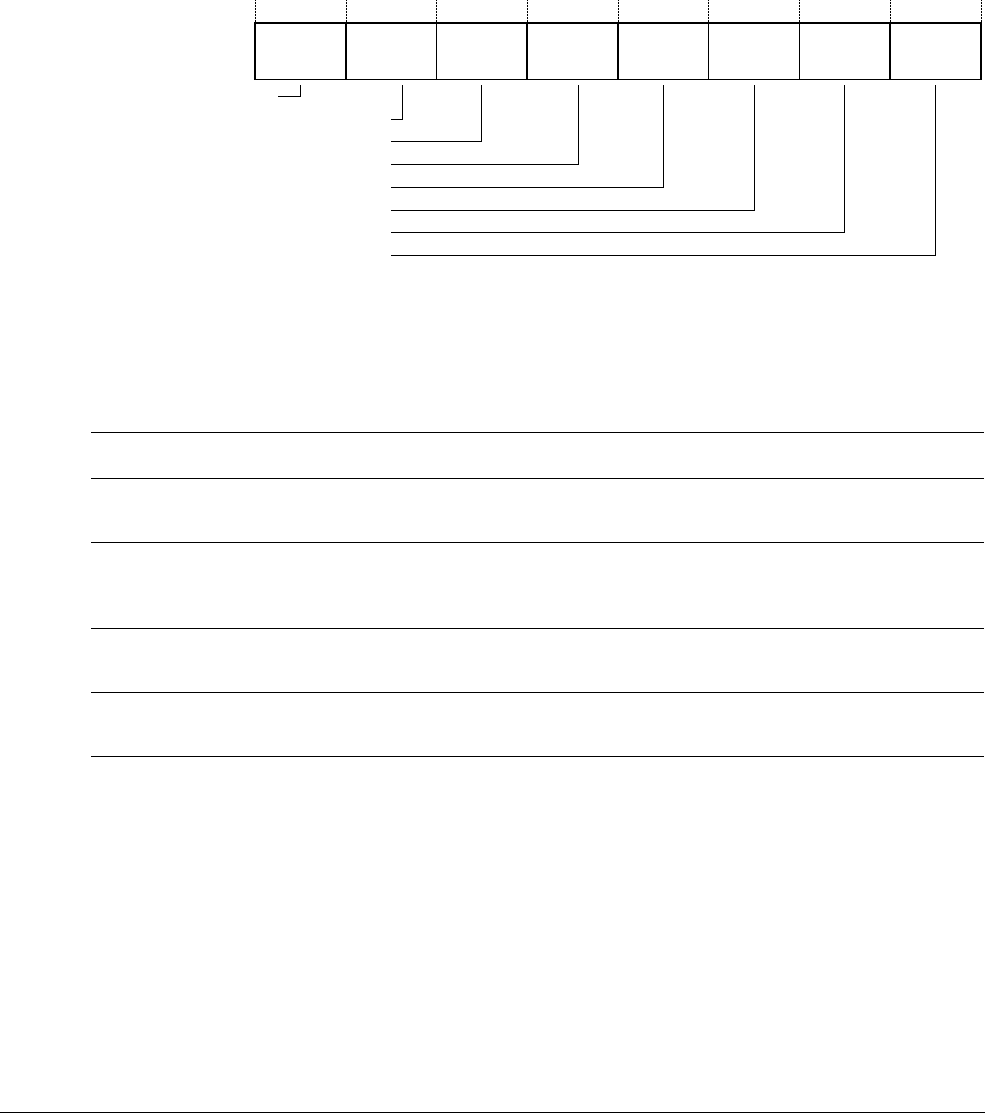

Figure 4-22 shows the bit arrangement for Instruction Set Attributes Register 3.

Figure 4-22 Instruction Set Attributes Register 3 format

Table 4-17 shows how the bit values correspond with the Instruction Set Attributes Register 3

functions.

31 28 27 24 23 20 19 16 15 12 11 8 7 4 3 0

ThumbEE extension

True NOP instructions

Thumb copy instructions

Table branch instructions

Synchronization primitive instructions

SVC instructions

SIMD instructions

Saturate instructions

Table 4-17 Instruction Set Attributes Register 3 bit functions

Bits Field Function

[31:28] ThumbEE

extension

Indicates support for ThumbEE Execution Environment extension.

0x0

, no support.

[27:24] True NOP

instructions

Indicates support for true

NOP

instructions.

0x1

, the processor supports

NOP16

,

NOP32

and various

NOP

compatible hints in both the ARM

and Thumb instruction sets.

[23:20] Thumb copy

instructions

Indicates support for Thumb copy instructions.

0x1

, the processor supports Thumb

MOV(3)

low register ⇒ low register.

[19:16] Table branch

instructions

Indicates support for table branch instructions.

0x1

, the processor supports table branch instructions,

TBB

and

TBH

.

[15:12] Synchronization

primitive

instructions

Indicates support for synchronization primitive instructions.

0x2

, the processor supports:

•

LDREX

and

STREX

•

LDREXB

,

LDREXH

,

LDREXD

,

STREXB

,

STREXH

,

STREXD

, and

CLREX

.