Processor Initialization, Resets, and Clocking

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 3-7

ID013010 Non-Confidential, Unrestricted Access

3.3 Reset modes

The reset signals in the processor enable you to reset different parts of the design independently.

Table 3-1 shows the reset signals, and the combinations and possible applications that you can

use them in.

Note

If nRESET is set to 1 and nSYSPORESET is set to 0 the behavior is architecturally

Unpredictable.

This section of the manual describes:

• Power-on reset

• Processor reset on page 3-8

• Normal operation on page 3-8

• Halt operation on page 3-8.

3.3.1 Power-on reset

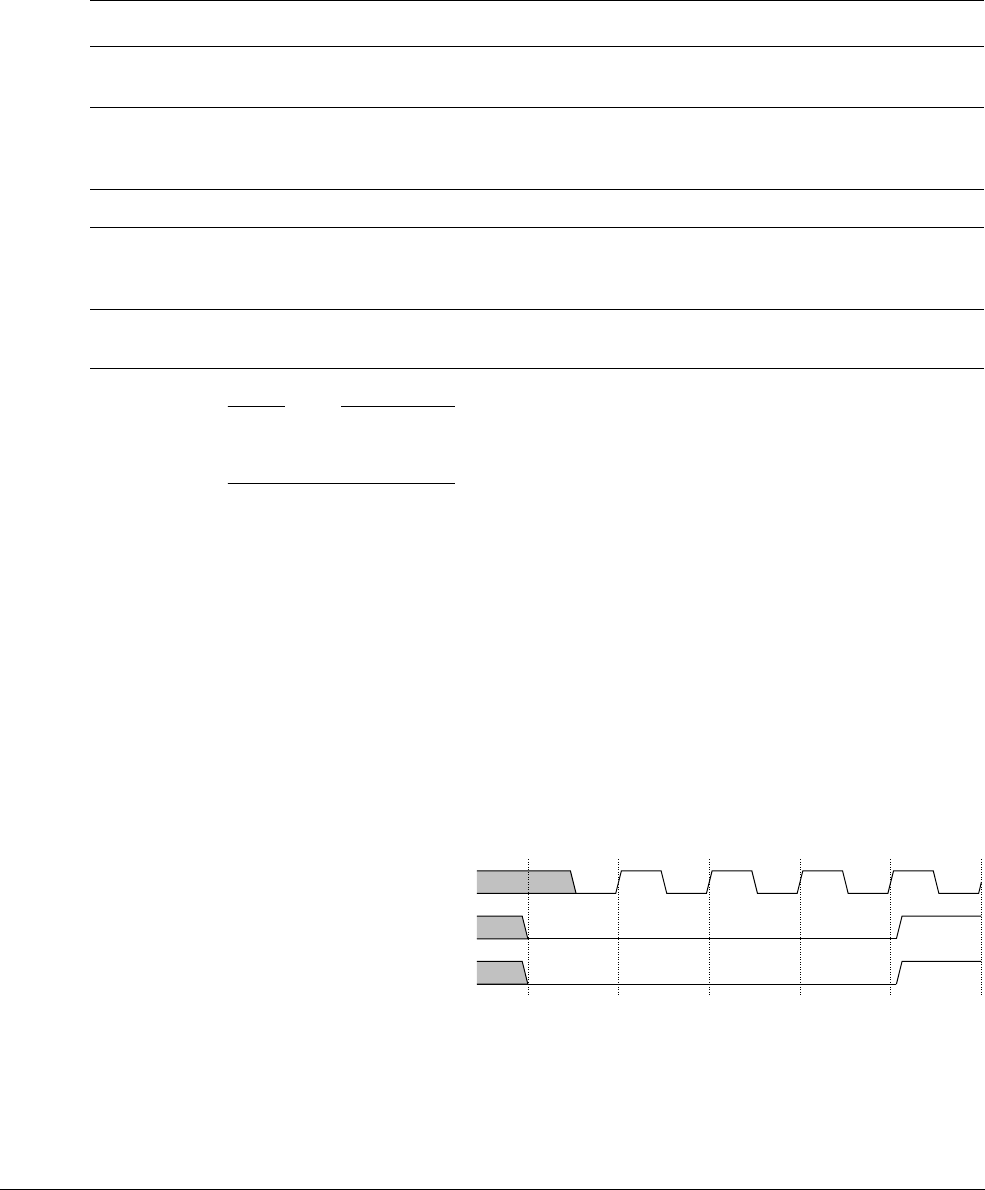

You must apply power-on or cold reset to the processor when power is first applied to the

system. In the case of power-on reset, the leading, or falling, edge of the reset signals, nRESET

and nSYSPORESET, does not have to be synchronous to CLKIN. Because the nRESET and

nSYSPORESET signals are synchronized within the processor, you do not have to synchronize

these signals. Figure 3-1 shows the application of power-on reset.

Figure 3-1 Power-on reset

ARM recommends that you assert the reset signals for at least four CLKIN cycles to ensure

correct reset behavior.

It is not necessary to assert PRESETDBGn on power-up.

Table 3-1 Reset modes

Reset mode nRESET PRESETDBGn nSYSPORESET nCPUHALT Application

Power-on reset 0 x 0 x Reset at power up, full system

reset. Hard reset or cold reset.

Processor reset 0 x 1 x Reset of processor only,

watchdog reset. Soft reset or

warm reset.

Normal 1 x 1 1 Normal run mode.

Halt 1 x 1 0 Halt mode, provided normal

mode has not been entered

since reset.

Debug reset x 0 x x Resets all debug logic and

debug APB interface.

CLKIN

nRESET

nSYSPORESET