System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-24

ID013010 Non-Confidential, Unrestricted Access

c0, Memory Model Feature Register 2, MMFR2

The Memory Model Feature Register 2 provides information about the memory model, memory

management, and cache support operations of the processor.

The Memory Model Feature Register 2 is:

• a read-only register

• accessible in Privileged mode only.

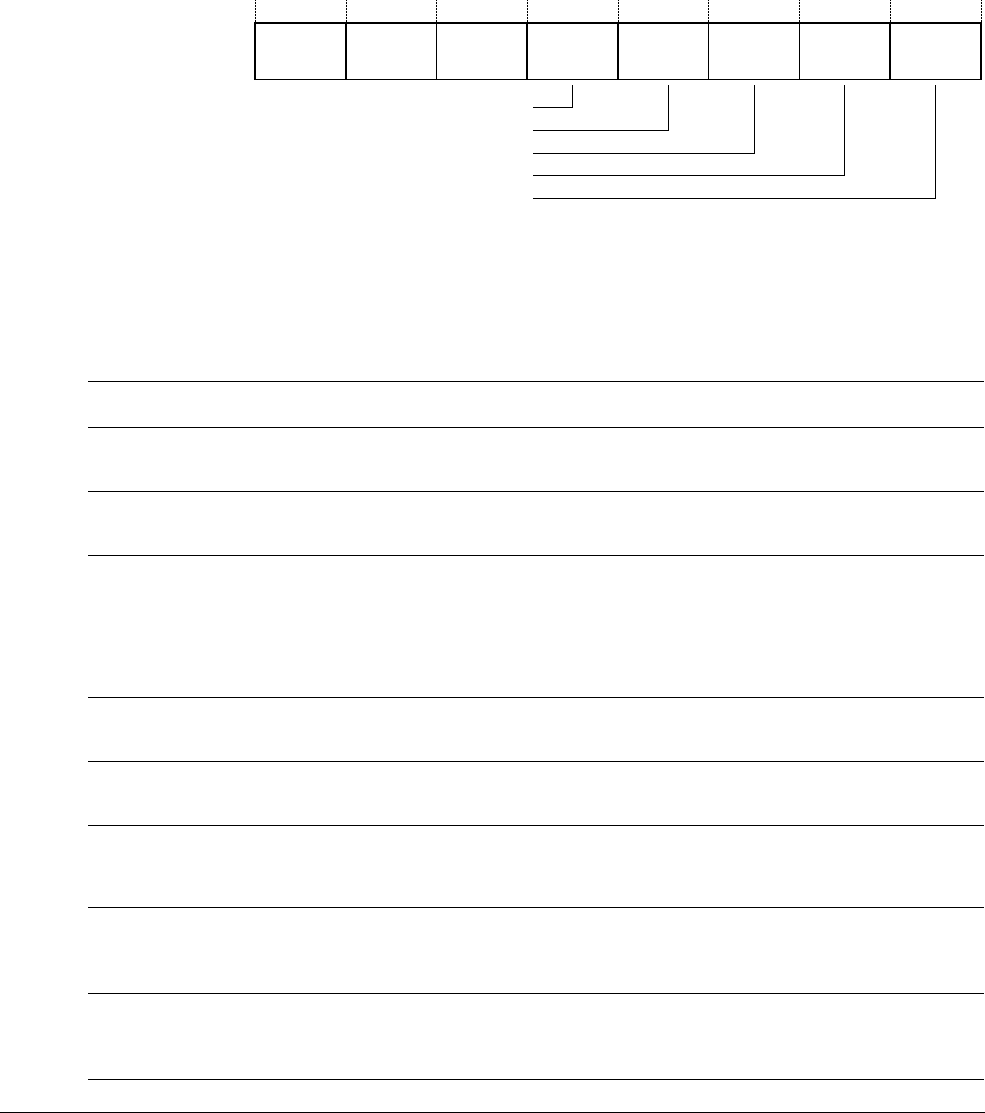

Figure 4-17 shows the bit arrangement for Memory Model Feature Register 2.

Figure 4-17 Memory Model Feature Register 2 format

Table 4-12 shows how the bit values correspond with the Memory Model Feature Register 2

functions.

31 28 27 24 23 20 19 16 15 12 11 8 7 4 3 0

Hardware

access flag

WFI

Memory

barrier

TLB maintenance operations (unified)

TLB maintenance operations (Harward)

L1 cache maintenance range operations (Harward)

L1 background prefetch cache operations

L1 foreground prefetch cache operations

Table 4-12 Memory Model Feature Register 2 bit functions

Bits Field Function

[31:28] Hardware access flag Indicates support for Hardware Access Flag.

0x0

, no support.

[27:24] WFI Indicates support for Wait-For-Interrupt stalling.

0x1

, the processor supports Wait-For-Interrupt.

[23:20] Memory barrier Indicates support for memory barrier operations.

0x2

, the processor supports:

• DSB (formerly DWB)

• ISB (formerly Prefetch Flush)

•DMB.

[19:16] TLB maintenance

operations (unified)

Indicates support for TLB maintenance operations, unified architecture.

0x0

, no support.

[15:12] TLB maintenance

operations (Harvard)

Indicates support for TLB maintenance operations, Harvard architecture.

0x0

, no support.

[11:8] L1 cache

maintenance range

operations (Harvard)

Indicates support for cache maintenance range operations, Harvard architecture.

0x0

, no support.

[7:4] L1 background

prefetch cache

operations

Indicates support for background prefetch cache range operations, Harvard

architecture.

0x0

, no support.

[3:0] L1 foreground

prefetch cache

operations

Indicates support for foreground prefetch cache range operations, Harvard

architecture.

0x0

, no support.