Events and Performance Monitor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 6-7

ID013010 Non-Confidential, Unrestricted Access

6.3 Performance monitoring registers

The performance monitoring registers are described in:

• c9, Performance Monitor Control Register

• c9, Count Enable Set Register on page 6-8

• c9, Count Enable Clear Register on page 6-9

• c9, Overflow Flag Status Register on page 6-10

• c9, Software Increment Register on page 6-11

• c9, Performance Counter Selection Register on page 6-12

• c9, Cycle Count Register on page 6-13

• c9, Event Selection Register on page 6-13

• c9, Performance Monitor Count Registers on page 6-15

• c9, User Enable Register on page 6-15

• c9, Interrupt Enable Set Register on page 6-16

• c9, Interrupt Enable Clear Register on page 6-17.

6.3.1 c9, Performance Monitor Control Register

The Performance MoNitor Control (PMNC) Register controls the operation of the three count

registers, and the CCNT Register.

The PMNC Register is:

• A read/write register.

• Always accessible in Privileged mode. The USEREN Register determines accessibility in

User mode, see c9, User Enable Register on page 6-15.

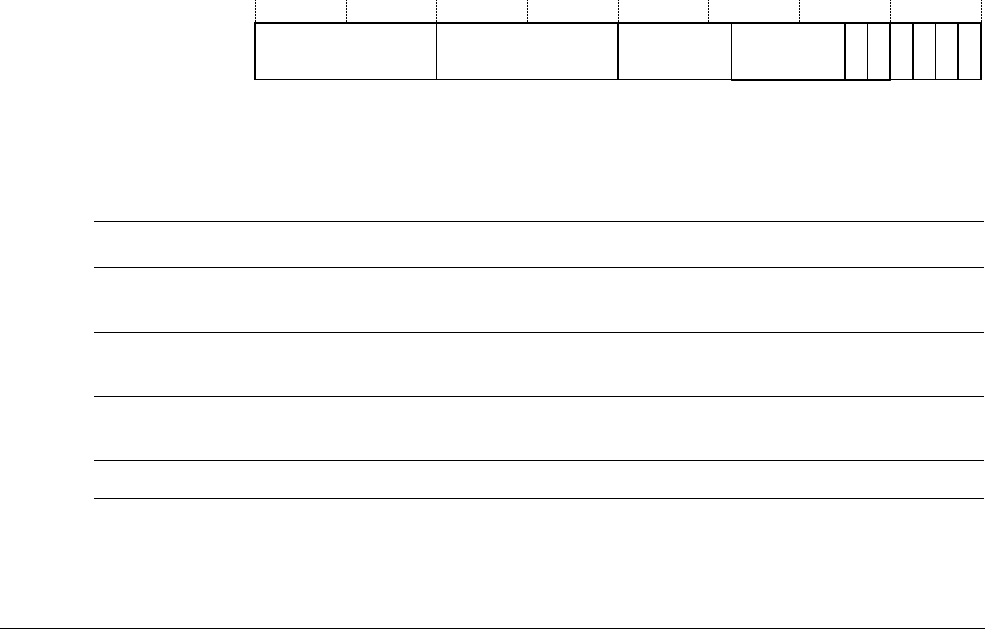

Figure 6-1 shows the bit arrangement for the PMNC Register.

Figure 6-1 PMNC Register format

Table 6-2 shows how the bit values correspond with the PMNC Register.

D C P EIMP

31 11 6 43210

IDCODE N

10

Reserved

D

P

5

X

24 23 16 15

Table 6-2 PMNC Register bit functions

Bits Field Function

[31:24] IMP Implementer code:

0x41

= ARM

[23:16] IDCODE Identification code:

0x14

= Cortex-R4

[15:11] N Specifies the number of counters implemented:

0x3

= three counters implemented

[10: 6] Reserved RAZ on reads, Should Be Zero or Preserved (SBZP) on writes

[5] DP Disable CCNT when prohibited, that is, when non-invasive debug is not enabled:

0 = Count is enabled in prohibited regions. This is the reset value.

1 = Count is disabled in prohibited regions.