System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-33

ID013010 Non-Confidential, Unrestricted Access

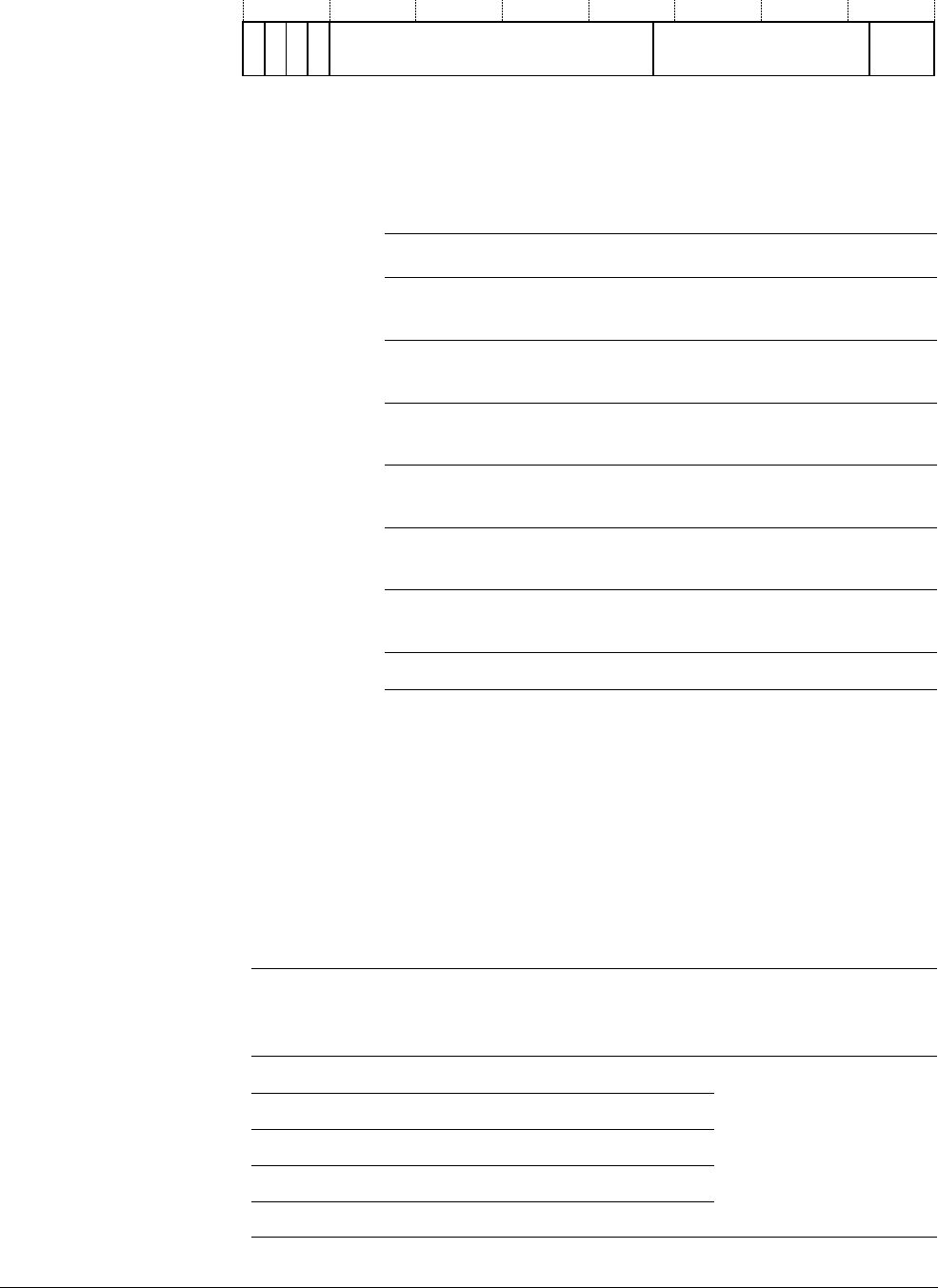

Figure 4-24 Current Cache Size Identification Register format

Table 4-19 shows how the bit values correspond with the Current Cache Size Identification

Register.

The LineSize field is encoded as 2 less than log(2) of the number of words in the cache line. For

example, a value of

0x0

indicates there are four words in a cache line, that is the minimum size

for the cache. A value of

0x1

indicates there are eight words in a cache line.

Table 4-20 shows the individual bit field and complete register encodings for the Current Cache

Size Identification Register. Use this to match the cache size and level of cache set by the

Current Cache Size Selection Register (CSSR). See c0, Cache Size Selection Register on

page 4-35.

Line

Size

W

T

31 30 29 28 27 13 12 2 0

W

B

R

A

W

A

NumSets Associativity

Table 4-19 Current Cache Size Identification Register bit functions

Bits Field Function

[31] WT Indicates support available for write-through:

1 = write-through support available

a

a. See Table 4-20 for valid bit field encodings.

[30] WB Indicates support available for write-back:

1 = write-back support available

a

[29] RA Indicates support available for read allocation:

1 = read allocation support available

a

[28] WA Indicates support available for write allocation:

1 = write allocation support available

a

[27:13] NumSets Indicates the number of sets as

(number of sets) - 1

a

[12:3] Associativity Indicates the number of ways as

(number of ways) - 1

a

[2:0] LineSize

Indicates the number of words in each cache line

a

Table 4-20 Bit field and register encodings for Current Cache Size Identification Register

Size

Complete

register

encoding

Register bit field encoding

WT WB RA WA NumSets Associativity LineSize

4KB

0xF003E019

1111

0x001F 0x3 0x1

8KB

0xF007E019

1111

0x003F

16KB

0xF00FE019

1111

0x007F

32KB

0xF01FE019

1111

0x00FF

64KB

0xF03FE019

1111

0x01FF