System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-56

ID013010 Non-Confidential, Unrestricted Access

Figure 4-39 c7 format for Set and Way

Table 4-36 shows how the bit values correspond with the Cache Operation functions for Set and

Way format operations.

Table 4-37 shows the cache sizes and the resultant bit range for Set.

See c0, Cache Type Register on page 4-15 for more information on cache sizes.

Address format

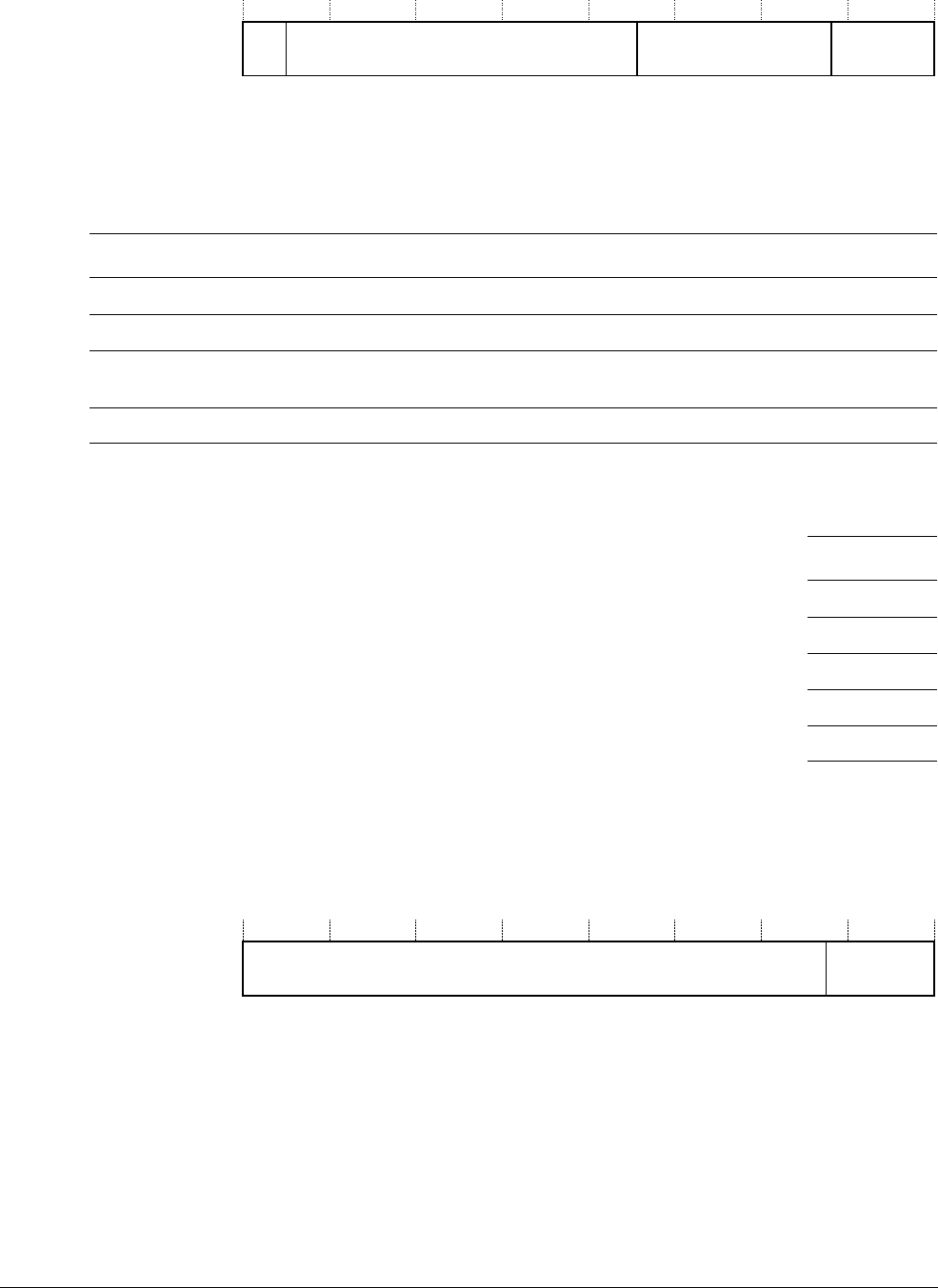

Figure 4-40 shows the address format for invalidate and clean operations.

Figure 4-40 Cache operations address format

Way

0

Set ReservedReserved

54S+4S+531 2930

Table 4-36 Functional bits of c7 for Set and Way

Bits Field Function

[31:30] Way Indicates the cache way to invalidate or clean.

[29:S+5] Reserved SBZ.

[S+4:5] Set Indicates the cache set to invalidate or clean. Because the cache sizes are configurable, the width

of the Set field is unique to the cache size. See Table 4-37.

[4:0]] Reserved SBZ.

Table 4-37 Widths of the set field for L1 cache sizes

Size Set

4KB [9:5]

8KB [10:5]

16KB [11:5]

32KB [12:5]

64KB [13:5]

Address

31

4

0

Reserved

5