System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-25

ID013010 Non-Confidential, Unrestricted Access

To access the Memory Model Feature Register 2 read CP15 with:

MRC p15, 0, <Rd>, c0, c1, 6 ; Read Memory Model Feature Register 2.

c0, Memory Model Feature Register 3, MMFR3

The Memory Model Feature Register 3 provides information about the two cache line

maintenance operations for the processor.

The Memory Model Feature Register 3 is:

• a read-only register

• accessible in Privileged mode only.

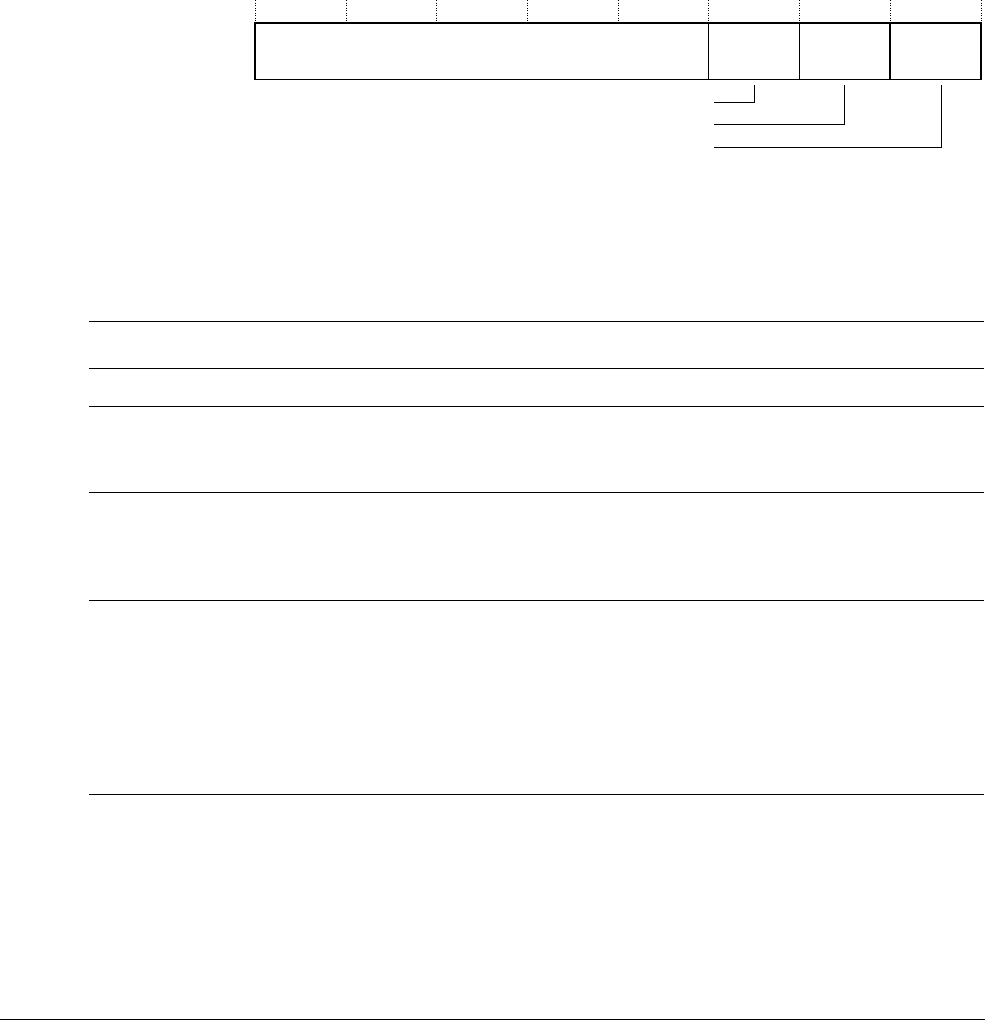

Figure 4-18 shows the bit arrangement for Memory Model Feature Register 3.

Figure 4-18 Memory Model Feature Register 3 format

Table 4-13 shows how the bit values correspond with the Memory Model Feature Register 3

functions.

To access the Memory Model Feature Register 3 read CP15 with:

MRC p15, 0, <Rd>, c0, c1, 7 ; Read Memory Model Feature Register 3.

31 8 7 3 0

Reserved

412 11

Branch predictor maintenance operations

Hierarchical cache maintenance operations by Set and Way

Hierarchical cache maintenance operations by MVA

Table 4-13 Memory Model Feature Register 3 bit functions

Bits Field Function

[31:12] Reserved SBZ.

[11:8] Branch predictor maintenance

operations

Indicates support for branch predictor maintenance operations in systems

with hierarchical cache maintenance operations.

0x0

, no support.

[7:4] Hierarchical cache maintenance

operations by Set and Way

Indicates support for hierarchical cache maintenance operations by Set and

Way.

0x1

, the processor supports invalidate cache, clean and invalidate, and clean

by Set and Way.

[3:0] Hierarchical cache maintenance

operations by MVA

Indicates support for hierarchical cache maintenance operations by address.

0x1

, the processor supports:

• Invalidate data cache by address

• Clean data cache by address

• Clean and invalidate data cache by address

• Invalidate instruction cache by address

• Invalidate all instruction cache entries.