Debug

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 11-42

ID013010 Non-Confidential, Unrestricted Access

Table 11-40 shows the values in the link register after exceptions.

The following sections describe:

• Effect of debug exceptions on CP15 registers and WFAR

• Avoiding unrecoverable states on page 11-43.

11.7.1 Effect of debug exceptions on CP15 registers and WFAR

The four CP15 registers that record abort information are:

1. Data Fault Address Register (DFAR)

2. Instruction Fault Address Register (IFAR)

3. Instruction Fault Status Register (IFSR)

4. Data Fault Status Register (DFSR).

For more information on these registers, see Chapter 4 System Control Coprocessor.

If the processor takes a debug exception because of a watchpoint debug event, the processor

performs the following actions on these registers:

• it does not change the IFSR or IFAR

• it updates the DFSR with the debug event encoding

• it writes an Unpredictable value to the DFAR

• it updates the WFAR with the address of the instruction that accessed the watchpointed

address, plus a processor state dependent offset:

— + 8 for ARM state

— + 4 for Thumb state.

If the processor takes a debug exception because of a breakpoint,

BKPT

, or vector catch debug

event, the processor performs the following actions on these registers:

• it updates the IFSR with the debug event encoding

• it writes an Unpredictable value to the IFAR

• it does not change the DFSR, DFAR, or WFAR.

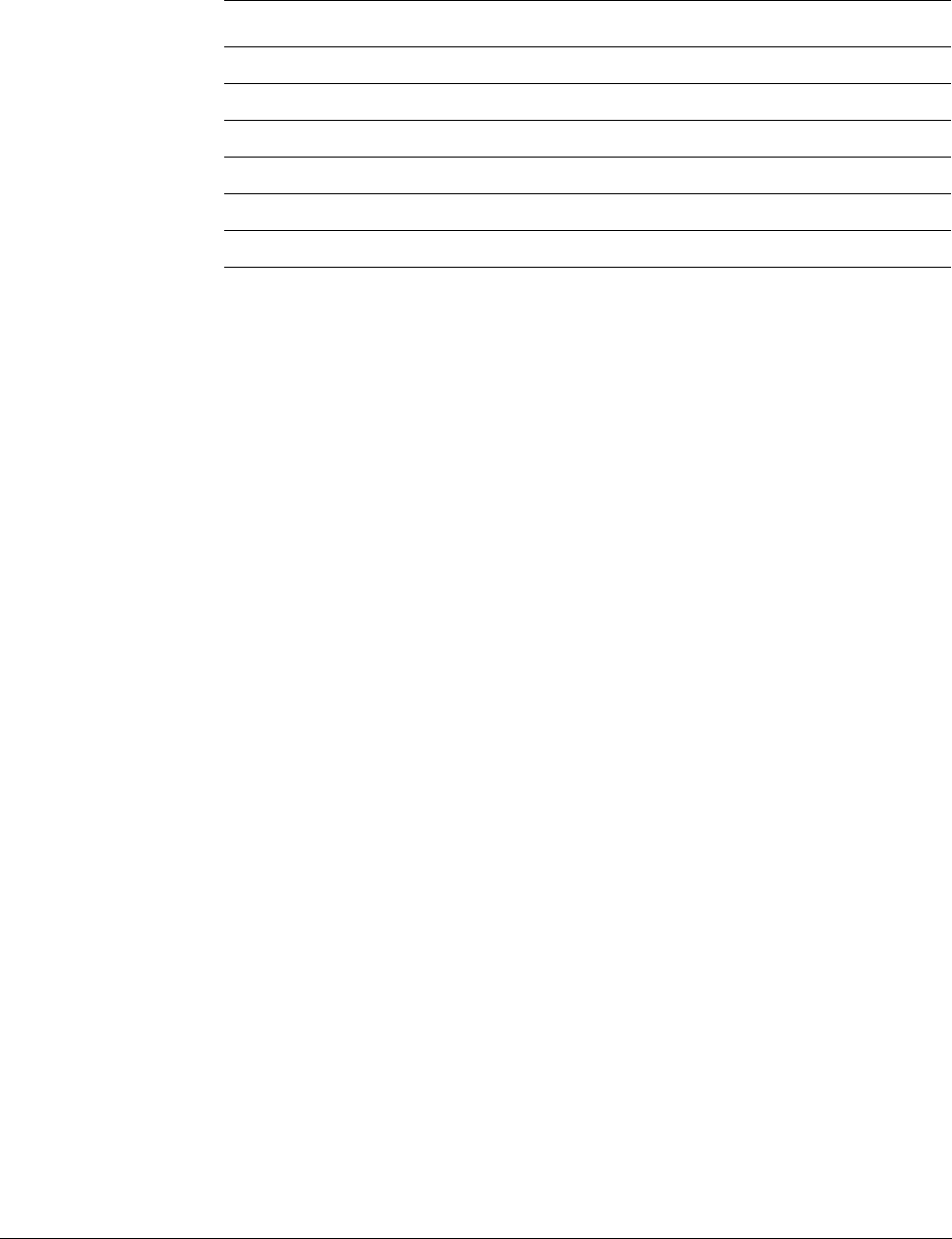

Table 11-40 Values in link register after exceptions

Cause of fault ARM Thumb

Return address (RA

a

) meaning

a. This is the address of the instruction that the processor can execute first on debug exception return. The

address of the access that hit the watchpoint is in the WFAR.

Breakpoint RA+4 RA+4 Breakpointed instruction address

Watchpoint RA+8 RA+8 Watchpointed instruction address

BKPT

instruction RA+4 RA+4

BKPT

instruction address

Vector catch RA+4 RA+4 Vector address

Prefetch Abort RA+4 RA+4 Address of the instruction where the execution can resume

Data Abort RA+8 RA+8 Address of the instruction where the execution can resume