FPU Programmer’s Model

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 12-9

ID013010 Non-Confidential, Unrestricted Access

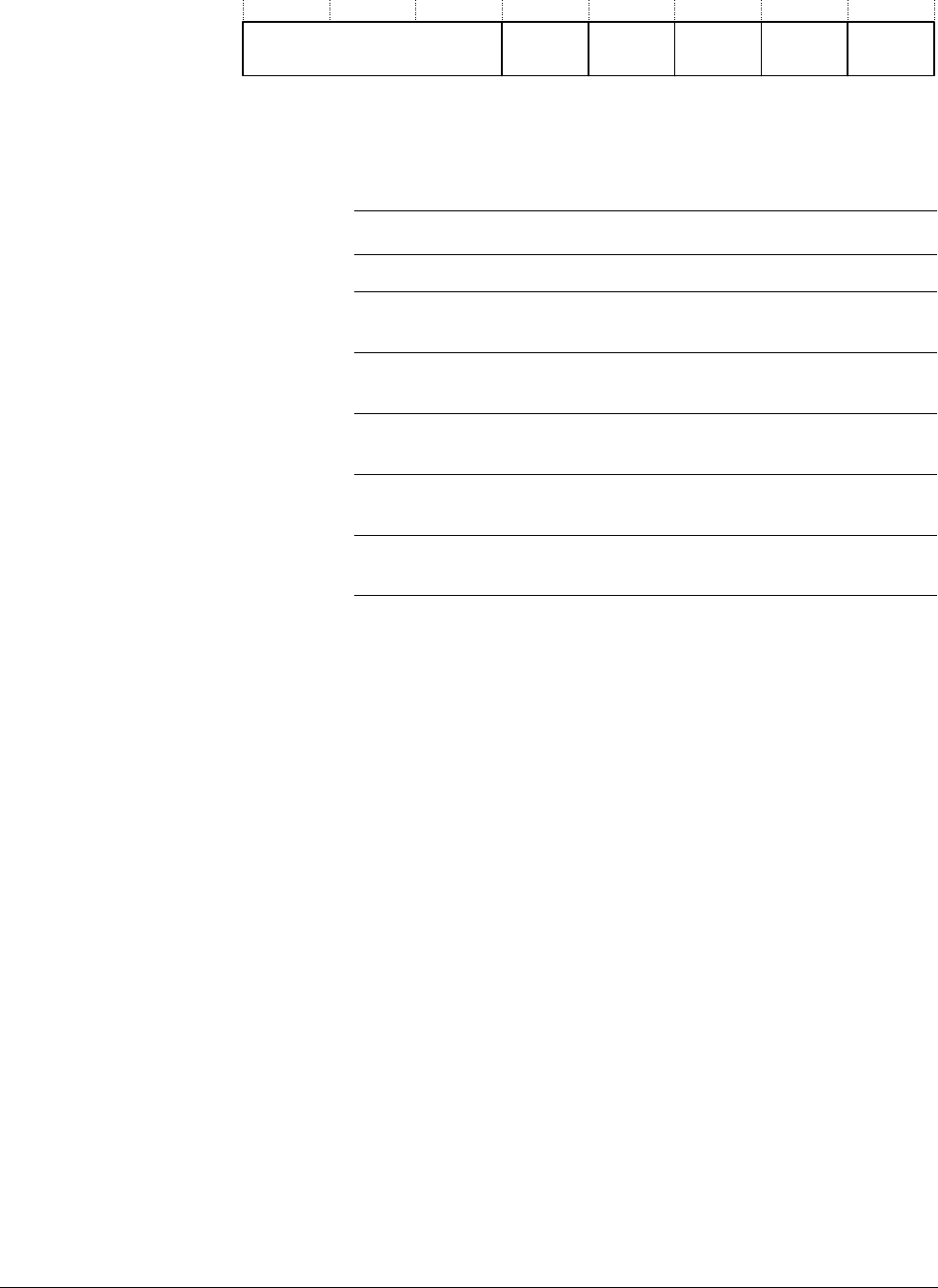

Figure 12-6 MVFR1 Register format

Table 12-7 shows how the bit values correspond with the MVFR1 Register.

FZ

Reserved I DNSP LS

31 20 19 16 15 12 11 8 7 4 3 0

Table 12-7 MVFR1 Register bit functions

Bits Field Function

[31:20] - Reserved

[19:16] SP Single-precision floating-point operations supported for VFP:

0b0000

= not supported

[15:12] I Integer operations supported for VFP:

0b0000

= not supported

[11:8] LS Load and store instructions supported for VFP:

0b0000

= not supported

[7:4] DN Propagation of NaN values supported for VFP:

0x1

[3:0] FZ Full denormal arithmetic supported for VFP:

0x1