System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-68

ID013010 Non-Confidential, Unrestricted Access

To access the nVAL Reset Enable Clear Register, read or write CP15 with:

MRC p15, 0, <Rd>, c15, c1, 6 ; Read nVAL Reset Enable Clear Register

MCR p15, 0, <Rd>, c15, c1, 6 ; Write nVAL Reset Enable Clear Register

On reads, this register returns the current setting. On writes, overflow reset requests that are

currently enabled can be disabled.

For more information of how to enable reset requests on counter overflows, and how the

requests are signaled, see c15, nVAL Reset Enable Set Register on page 4-64.

c15, nVAL Debug Request Enable Clear Register

The nVAL Debug Request Enable Clear Register disables overflow debug requests from any of

the PMC Registers, PMC0-PMC2, and CCNT, that are enabled.

The nVAL Debug Request Enable Clear Register is:

• A read/write register.

• Always accessible in Privileged mode. The USEREN Register determines access, see c9,

User Enable Register on page 6-15.

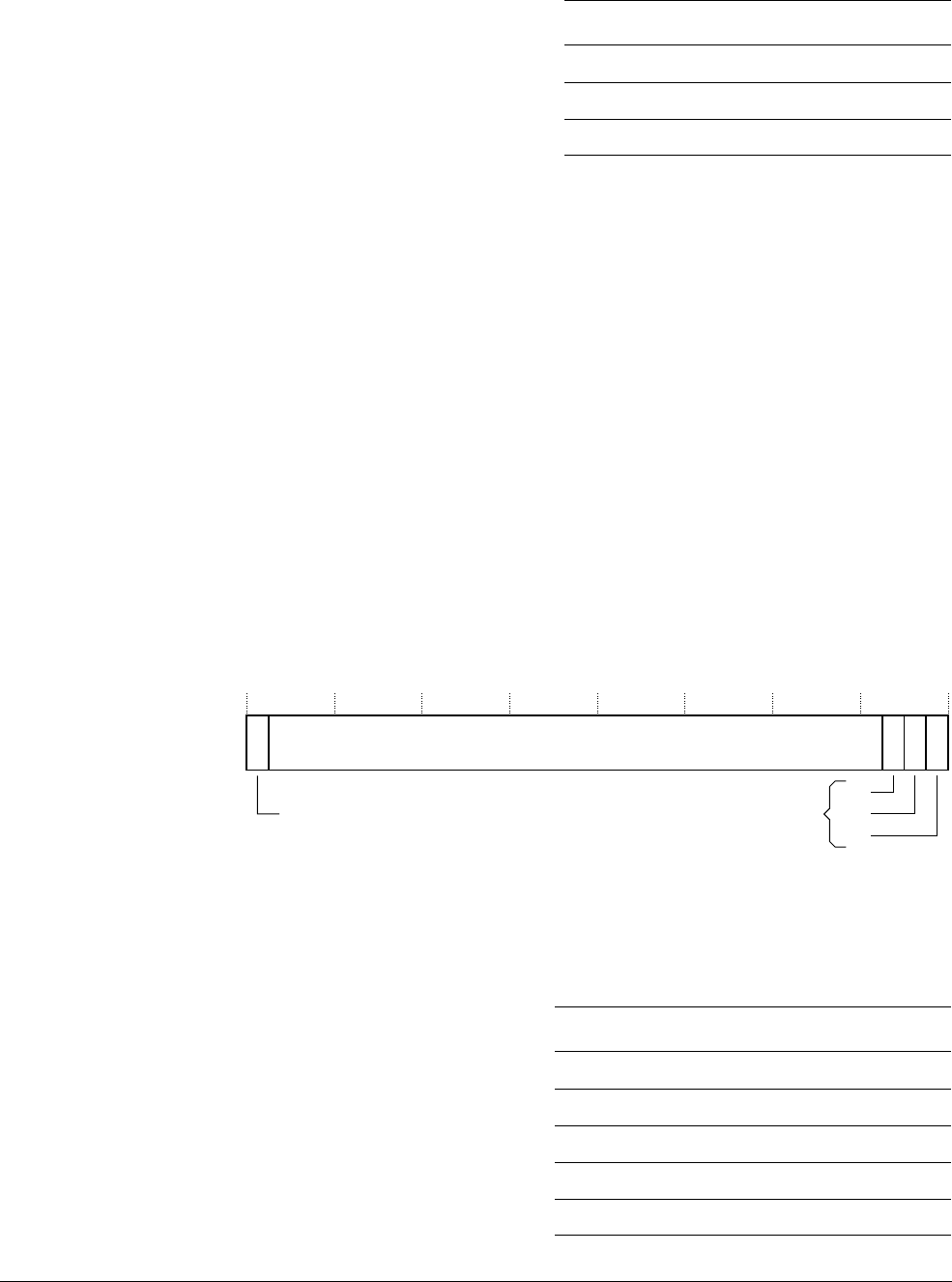

Figure 4-51 shows the bit arrangement for the nVAL Debug Request Enable Clear Register.

Figure 4-51 nVAL Debug Request Enable Clear Register format

Table 4-49 shows how the bit values correspond with the nVAL Debug Request Enable Clear

Register.

[2] P2 PMC2 overflow reset request

[1] P1 PMC1 overflow reset request

[0] P0 PMC0 overflow reset request

Table 4-48 nVAL Reset Enable Clear Register bit functions (continued)

Bits Field Function

C

31 3210

Reserved

P2

P1

P0

Performance monitor counter overflow

debug request disables

Cycle count overflow

debug request disable

Table 4-49 nVAL Debug Request Enable Clear Register bit functions

Bits Field Function

[31] C CCNT overflow debug request

[30:3] Reserved UNP or SBZP

[2] P2 PMC2 overflow debug request

[1] P1 PMC1 overflow debug request

[0] P0 PMC0 overflow debug request