Debug

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 11-11

ID013010 Non-Confidential, Unrestricted Access

The Debug ID Register is:

•in CP14 c0

• a 32 bit read-only register

• accessible in User and Privileged modes.

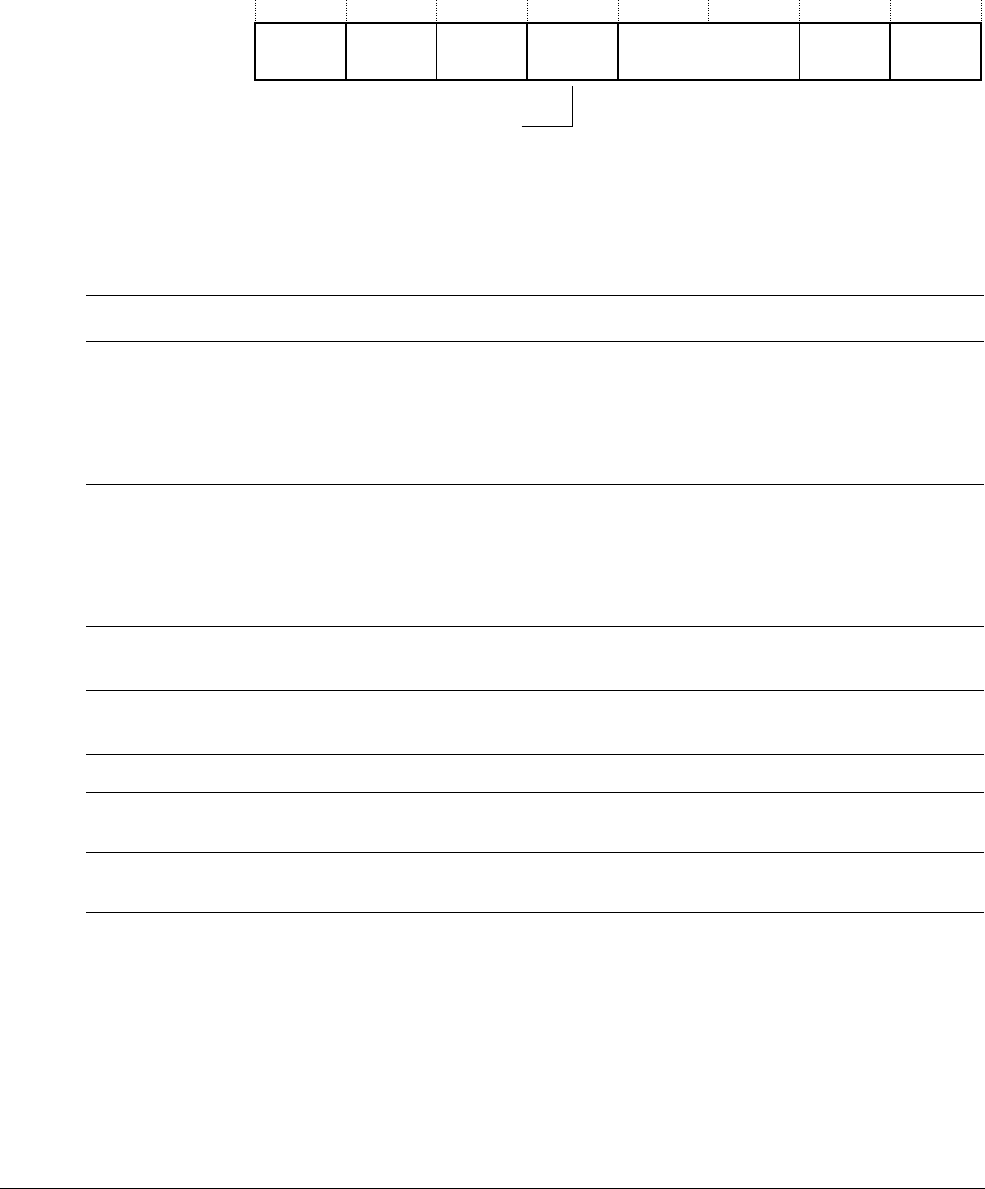

Figure 11-2 shows the bit arrangement of the DIDR.

Figure 11-2 Debug ID Register format

Table 11-7 shows how the bit values correspond with the Debug ID Register functions.

The values of the following fields of the Debug ID Register agree with the values in CP15 c0,

Main ID Register:

• DIDR[3:0] is the same as CP15 c0 bits [3:0]

• DIDR[7:4] is the same as CP15 c0 bits [23:20].

See c0, Main ID Register on page 4-14 for more information of CP15 c0, Main ID Register.

The reason for duplicating these fields here is that the Debug ID Register is also accessible

through the APB slave port. This enables an external debugger to determine the variant and

revision numbers without stopping the processor.

Reserved

WRP

31 28 27 24 23 20 19 16 15 4 3 0

BRP Context ID Variant Revision

Debug architecture

version

8

7

Table 11-7 Debug ID Register functions

Bits Field Function

[31:28] WRP Number of Watchpoint Register Pairs:

b0000 = 1 WRP

b0001 = 2 WRPs

...

b0111 = 8 WRPs.

[27: 24] BRP Number of Breakpoint Register Pairs:

b0001 = 2 BRPs

b0010 = 3 BRPs

...

b0111 = 8 BRPs.

[23:20] Context Number of Breakpoint Register Pairs with context ID comparison capability:

b0000 = 1 BRP has context ID comparison capability

[19:16] Debug architecture

version

Debug architecture version:

b0100 denotes ARMv7 Debug.

[15:8] Reserved RAZ.

[7: 4] Variant Implementation-defined variant number. See Product revision information on page 1-24

for details of the value of this field.

[3: 0] Revision Implementation-defined revision number. See Product revision information on

page 1-24 for details of the value of this field.