Events and Performance Monitor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 6-11

ID013010 Non-Confidential, Unrestricted Access

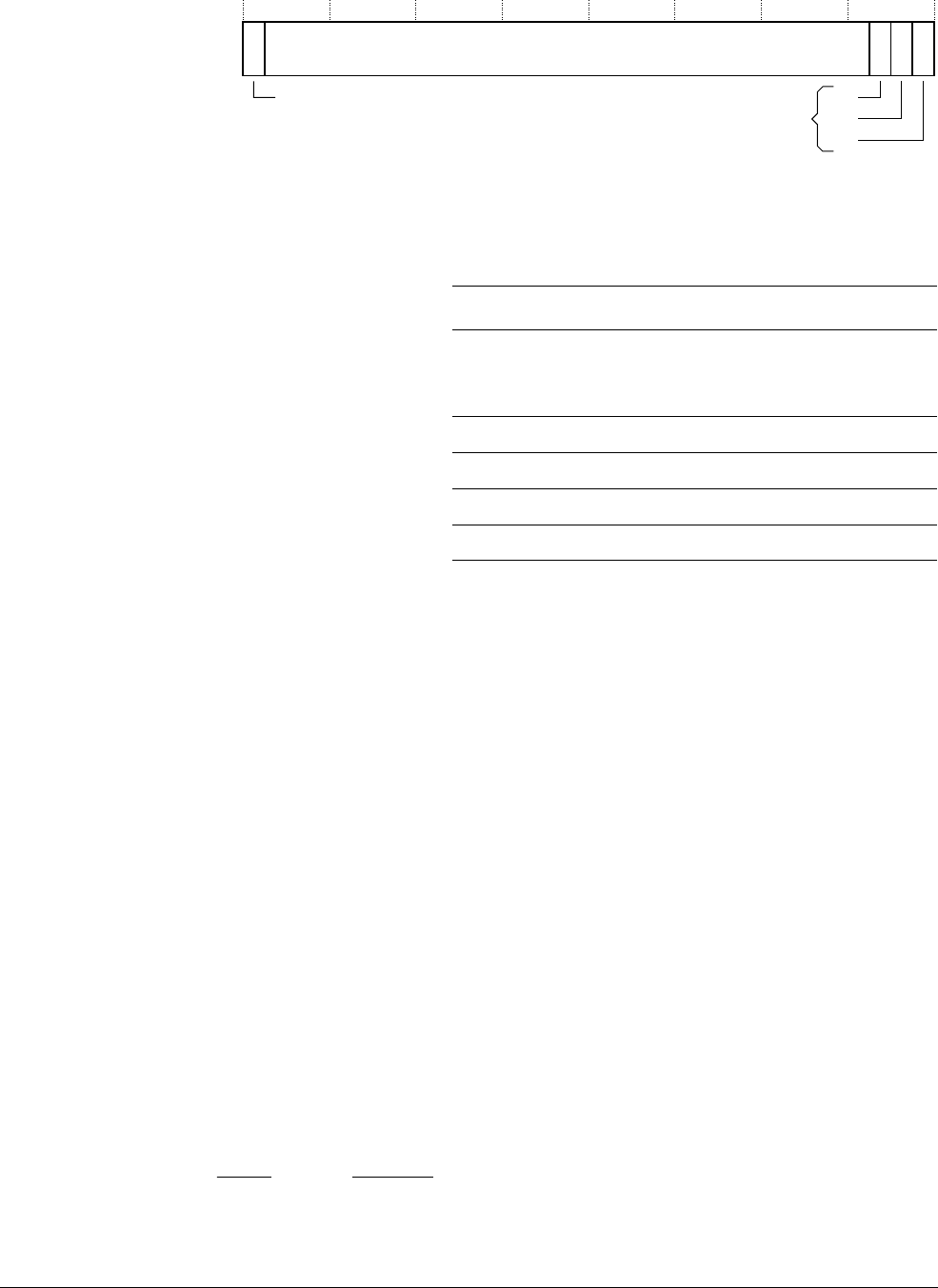

Figure 6-4 FLAG Register format

Table 6-5 shows how the bit values correspond with the FLAG Register.

To access the FLAG Register, read or write CP15 with:

MRC p15, 0, <Rd>, c9, c12, 3 ; Read FLAG Register

MCR p15, 0, <Rd>, c9, c12, 3 ; Write FLAG Register

If an overflow flag is set to 1 in the FLAG register it remains set until one of the following

happens:

• writing 1 to the flag bit in the FLAG Register clears the flag

• the processor is reset.

The following operations do not clear the overflow flags:

• disabling the overflowed counter in the CNTENC Register

• disabling all counters in the PMNC Register

• resetting the overflowed counter using the PMNC Register.

6.3.5 c9, Software Increment Register

The Software INCRement (SWINCR) Register increments the count of a Performance Monitor

Count Register.

The SWINCR Register is:

• A write-only register that Reads-As-Zero

• Always accessible in Privileged mode. The USEREN Register determine accessibility in

User mode, see c9, User Enable Register on page 6-15.

Caution

You must only use the SWINCR Register to increment performance monitor count registers

when the counter event is set to

0x00

, software count, in the Event Select Register, see c9, Event

Selection Register on page 6-13.

C

31 3210

Reserved

P2

P1

P0

Performance monitor counters

overflow flags

Cycle count overflow

Table 6-5 Overflow Flag Status Register bit functions

Bits Field Function

[31] Cycle counter overflow Cycle counter overflow flag:

0 = disable

1 = enable.

[30:3] Reserved UNP on reads, SBZP on writes

[2] P2 Counter 2 overflow flag

[1] P1 Counter 1 overflow flag

[0] P0 Counter 0 overflow flag