System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-13

ID013010 Non-Confidential, Unrestricted Access

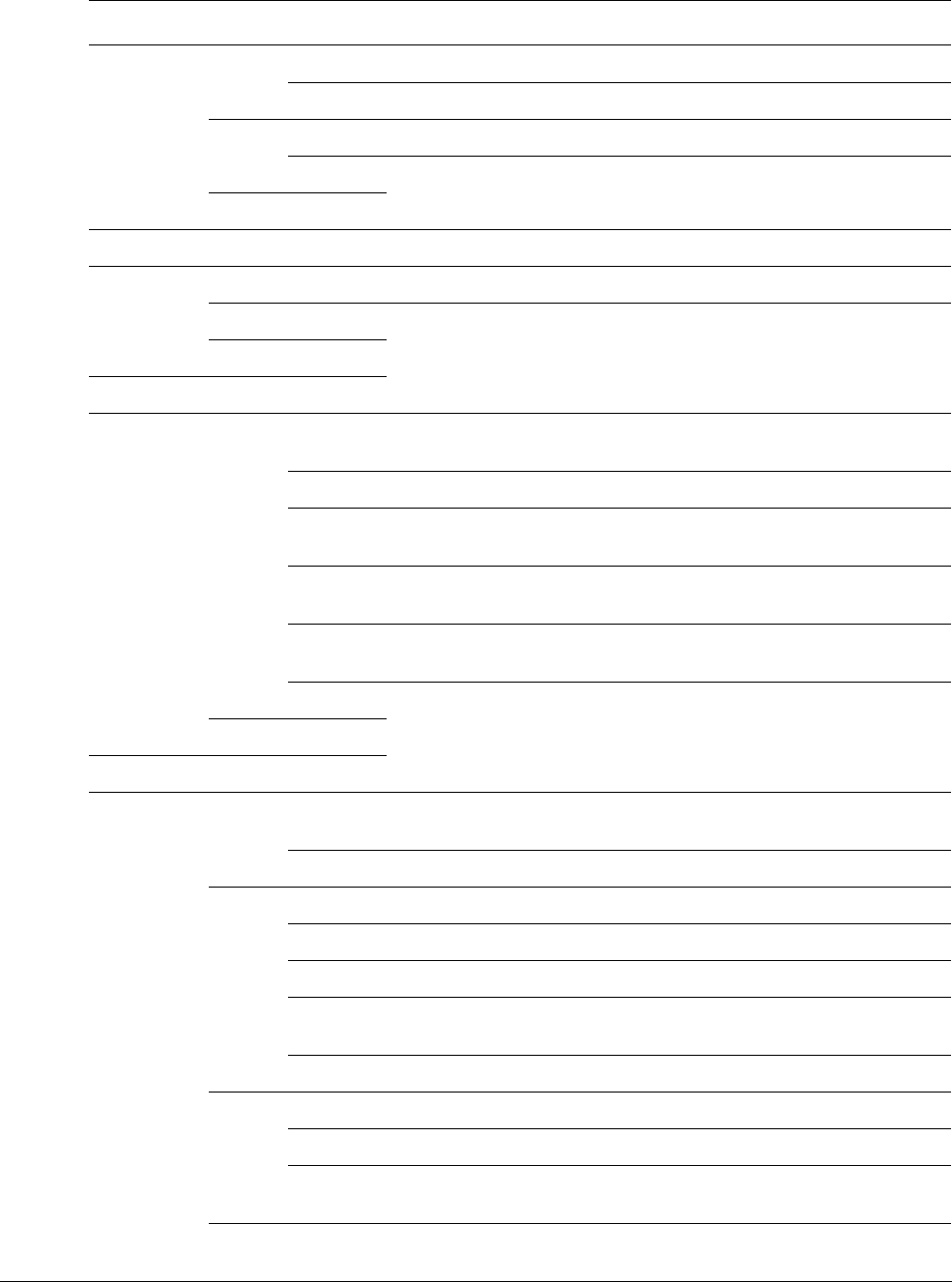

c14 0 User Enable Read/write

0x00000000

page 6-15

1 Interrupt Enable Set Read/write Unpredictable page 6-16

c14 2 Interrupt Enable Clear Read/write Unpredictable page 6-17

3-7 Undefined - - -

c15 0-7

c10 0 c0-c15 0-7 Undefined - - -

c11 0 c0 0 Slave Port Control Read/write

0x00000000

page 4-59

c0 1-7 Undefined - - -

c1-c15 0-7

c12 0 c0-c15 0-7

c13 0 c0 0 FCSE PID RAZ, ignore

writes

0x00000000

page 4-60

1 Context ID Read/write

0x00000000

page 4-60

2 User read/write

Thread and Process ID

Read/write

0x00000000

page 4-61

3 User Read-only

Thread and Process ID

Read/write

0x00000000

page 4-61

4 Privileged Only

Thread and Process ID

Read/write

0x00000000

page 4-61

5-7 Undefined - - -

c13 0 c1-c15 0-7 Undefined - - -

c14 0 c0-c15 0-7

c15 0 c0 0 Secondary Auxiliary

Control

Read/write

-

d

page 4-41

1-7 Undefined - - -

c1 0 nVAL IRQ Enable Set Read/write Unpredictable page 4-62

1 nVAL FIQ Enable Set Read/write Unpredictable page 4-63

2 nVAL Reset Enable Set Read/write Unpredictable page 4-64

3 nVAL Debug Request

Enable Set

Read/write Unpredictable page 4-64

4 nVAL IRQ Enable Clear Read/write Unpredictable page 4-65

c1 5 nVAL FIQ Enable Clear Read/write Unpredictable page 4-66

6 nVAL Reset Enable Clear Read/write Unpredictable page 4-67

7 nVAL Debug Request

Enable Clear

Read/write Unpredictable page 4-68

c2 0 Build Options 1 Read-only

-

d

page 4-72

Table 4-2 Summary of CP15 registers and operations (continued)

CRn Op1 CRm Op2 Register or operation Type Reset value Page