FPU Programmer’s Model

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 12-8

ID013010 Non-Confidential, Unrestricted Access

Table 12-5 shows how the bit values correspond with the FPEXC Register functions.

12.3.4 Media and VFP Feature Registers, MVFR0 and MVFR1

The VFP Feature Registers, MVFR0 and MVFR1, are read-only registers which describe the

features supported by the FPU. These registers are accessible in Privileged modes only.

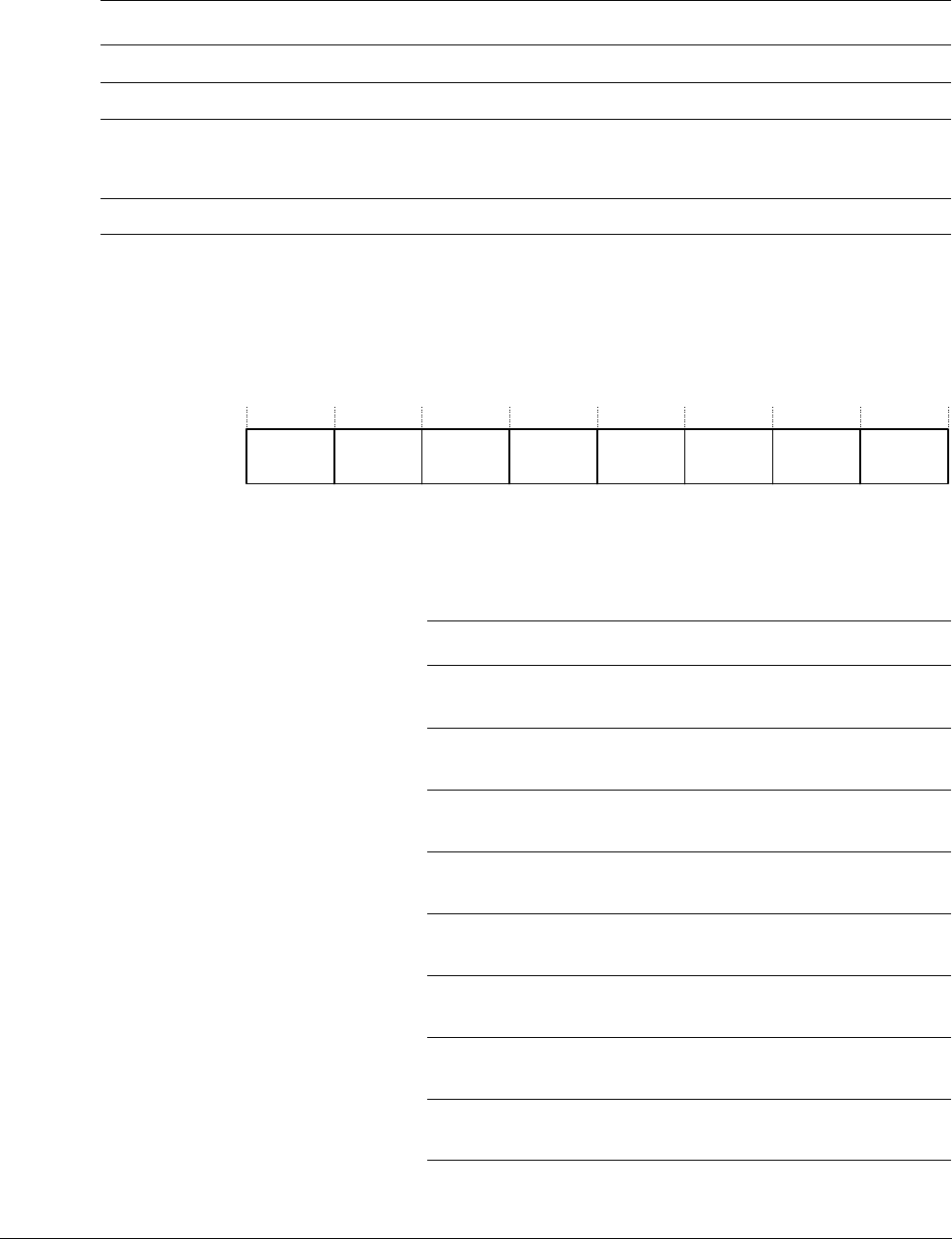

Figure 12-5 shows the bit arrangement of the MVFR0 Register.

Figure 12-5 MVFR0 Register format

Table 12-6 shows how the bit values correspond with the MVFR0 Register functions.

Figure 12-6 on page 12-9 shows the bit arrangement of the MVFR1 Register.

Table 12-5 Floating-Point Exception Register bit functions

Bits Field Function

[31] Reserved RAZ.

[30] EN VFP enable bit. Setting EN enables VFP functionality. Reset clears EN.

[29] DEX Set when an Undefined exception is taken because of a vector instruction that would have been

executed if the processor supported vectors. This field is cleared when an Undefined exception is

taken for any other reason. Resets to zero.

[28:0] Reserved RAZ.

RB

SVRM TE SPSR D DP

31 28 27 24 23 20 19 16 15 12 11 8 7 4 3 0

Table 12-6 MVFR0 Register bit functions

Bits Field Function

[31:28] RM All VFP rounding modes supported:

0x1

[27:24] SV VFP short vector unsupported:

0x0

[23:20] SR VFP hardware square root supported:

0x1

[19:16] D VFP hardware divide supported:

0x1

[15:12] TE Only untrapped exception handling can be selected:

0x0

[11:8] DP Double precision supported in VFPv3:

0x2

[7:4] SP Single precision supported in VFPv3:

0x2

[3:0] RB 16x64-bit media register bank supported:

0x1