Debug

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 11-23

ID013010 Non-Confidential, Unrestricted Access

11.4.12 Breakpoint Value Registers

Each BVR is associated with a Breakpoint Control Register (BCR). BCRy is the corresponding

control register for BVRy.

A pair of breakpoint registers, BVRy/BCRy, is called a Breakpoint Register Pair (BRP).

BVR0-7 are paired with BCR0-7 to make BRP0-7.

The breakpoint value contained in this register corresponds to either an instruction address or a

context ID. Breakpoints can be set on:

• an instruction address

• a context ID value

• an instruction address and context ID pair.

For an instruction address and context ID pair, two BRPs must be linked. A debug event is

generated when both the instruction address and the context ID pair match at the same time.

Table 11-16 shows how the bit values correspond with the Breakpoint Value Registers

functions.

Note

• Only BRPn supports context ID comparison, where n+1 is the number of breakpoint

register pairs implemented in the processor.

• Bits [1:0] of Registers BVR0 to BVR(n-1) are Do Not Modify on writes and

Read-As-Zero because these registers do not support context ID comparisons.

• The contents of the CP15 Context ID Register give the context ID value for a BVR to

match. For information on the Context ID Register, see Chapter 4 System Control

Coprocessor.

11.4.13 Breakpoint Control Registers

The BCR is a read/write register that contains the necessary control bits for setting:

• breakpoints

• linked breakpoints.

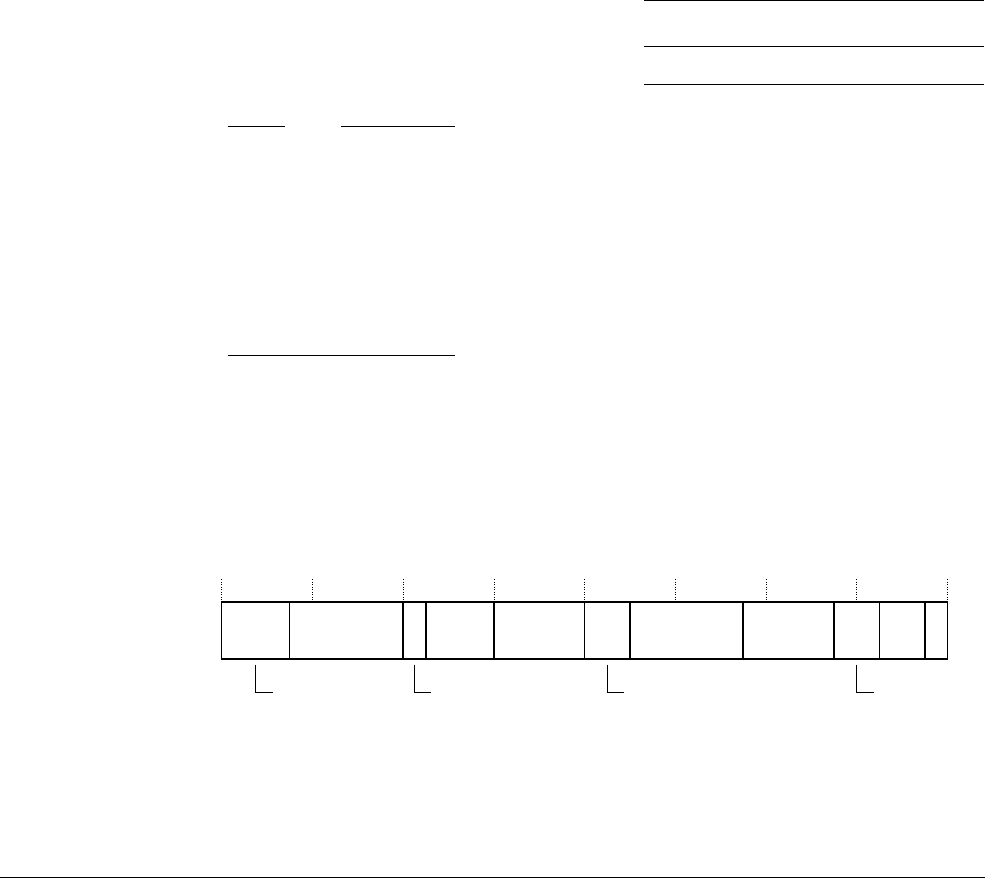

Figure 11-10 shows the bit arrangement of the BCRs.

Figure 11-10 Breakpoint Control Registers format

Table 11-16 Breakpoint Value Registers functions

Bits Reset value Description

[31:0]

0x0

Breakpoint value

Reserved

M Linked BRP Reserved

Byte

address

select

Secure state access control

Breakpoint

address mask

Reserved

Reserved

B

31 29 28 24 23 22 20 19 16 15 14 13 9 8 5 4 3 2 1 0

S