System Control Coprocessor

ARM DDI 0363E Copyright © 2009 ARM Limited. All rights reserved. 4-27

ID013010 Non-Confidential, Unrestricted Access

To access the Instruction Set Attributes Register 0, read CP15 with:

MRC p15, 0, <Rd>, c0, c2, 0 ; Read Instruction Set Attributes Register 0

c0, Instruction Set Attributes Register 1, ISAR1

The Instruction Set Attributes Register 1 provides information about the instruction set that the

processor supports beyond the basic set.

The Instruction Set Attributes Register 1 is:

• a read-only register

• accessible in Privileged mode only.

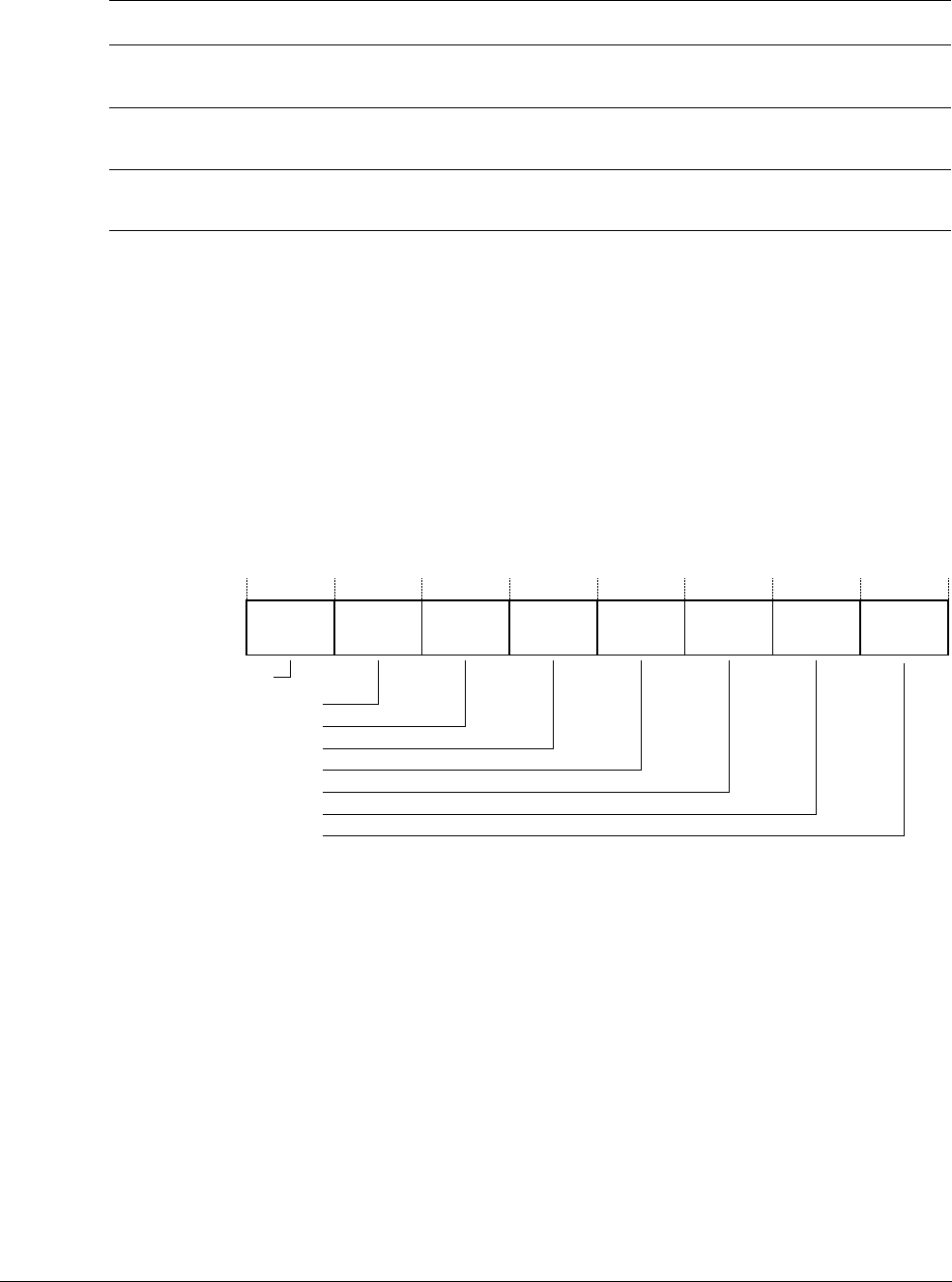

Figure 4-20 shows the bit arrangement for Instruction Set Attributes Register 1.

Figure 4-20 Instruction Set Attributes Register 1 format

[11:8] Bitfield instructions Indicates support for bitfield instructions.

0x1

, the processor supports bitfield instructions,

BFC

,

BFI

,

SBFX

, and

UBFX

.

[7:4] Bit counting instructions Indicates support for bit counting instructions.

0x1

, the processor supports

CLZ

.

[3:0] Atomic instructions Indicates support for atomic load and store instructions.

0x1

, the processor supports

SWP

and

SWPB

.

Table 4-14 Instruction Set Attributes Register 0 bit functions (continued)

Bits Field Function

31 28 27 24 23 20 19 16 15 12 11 8 7 4 3 0

Jazelle instructions

Interworking instructions

Immediate instructions

ITE instructions

Extend instructions

Exception 2 instructions

Exception 1 instructions

Endian instructions