CHAPTER 6 PERIPHERAL HARDWARE FUNCTION

173

User’s Manual U10676EJ3V0UM

6.4.6 Notes on using timer counter

(1) Error when timer starts

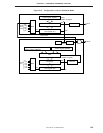

After the timer has been started (bit 3 of TMn has been set to “1”), the time required for generation of the match

signal, which is calculated by the expression (contents of modulo register + 1) × resolution, deviates by up

to one clock of the count pulse (CP). This is because timer counter count register Tn is cleared asynchronously

to CP, as shown below.

123 12

Timer startsTimer starts

Count pulse (CP)

Timer counter count

register (Tn)

0 0

If the frequency of CP is greater than one machine cycle, the time required for generation of the match signal,

which is calculated by the expression (modulo register contents + 1) × resolution, deviates by up to CP2 clock

after the timer has been started (bit 3 of TMn has been set to “1”). This is because Tn is cleared asynchronously

to CP, based on to CPU clock, as shown below.

112

Timer startsTimer starts

Count pulse (CP)

Timer counter count

register (Tn)

00

Remark n = 0 to 2