CHAPTER 4 INTERNAL CPU FUNCTION

73

User’s Manual U10676EJ3V0UM

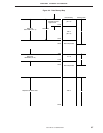

Figure 4-11. Data Saved to Stack Memory (MkII Mode)

Stack

SP – 1

SP

PUSH instruction

Stack

PC11-PC8

PC3-PC0

PC7-PC4

CALL, CALLA, CALLF instruction

Stack

Interrupt

SP – 4

SP – 3

SP – 2

SP – 5

PC11-PC8

PC3-PC0

PC7-PC4

SP – 2

SP – 1

SP

SP – 3

SP – 4

SP – 500

00

00

00

CY SK2

MBE RBE

SK1 SK0

IST0IST1

PSW

SP – 2

Register pair, low

Register pair, high

SP – 6 SP – 6

**

MBE RBE

**

**

Note

SP – 1

SP

Figure 4-12. Data Restored from Stack Memory (MkII Mode)

Stack

SP + 1

SP + 2

POP instruction

Stack

PC11-PC8

PC3-PC0

PC7-PC4

RET, RETS instruction

Stack

RETI instruction

SP + 2

SP + 3

SP + 4

SP + 1

PC11-PC8

PC3-PC0

PC7-PC4

SP + 4

SP + 5

SP + 6

SP + 3

SP + 2

SP + 100

00

00

00

CY SK2

MBE RBE

SK1 SK0

IST0IST1

PSW

SP

Register pair, low

Register pair, high

SP

SP

**

MBE RBE

**

**

Note

SP + 5

SP + 6

Note The contents of PSW other than MBE and RBE are not saved or restored.

Remark *: Undefined