16-bit Timers

11-37

[Note]

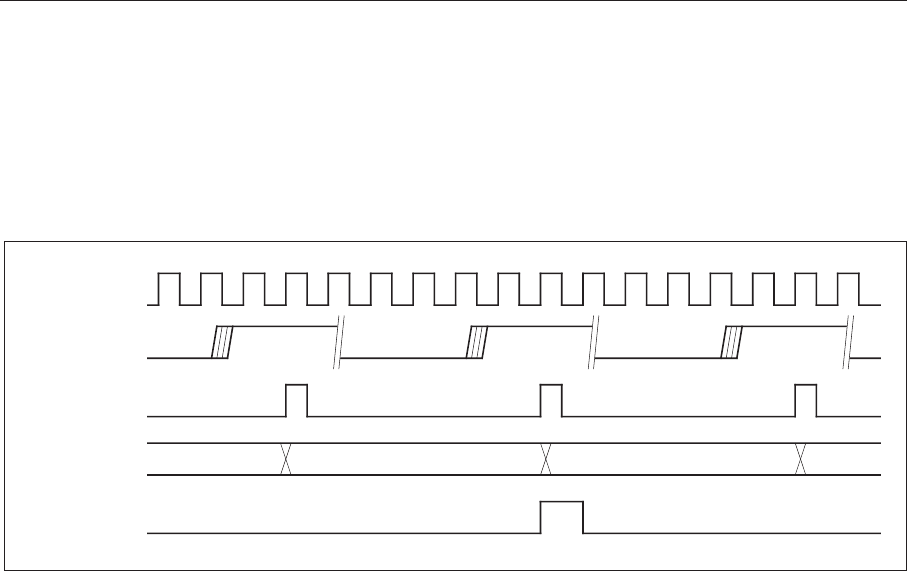

The pin input is sampled according to IOCLK. Input a signal with a pulse width of at least 6, 3, or 1.5 SYSCLK

cycles when (MCLK frequency/SYSCLK frequency) = 1, 2, or 4, respectively.

Also note that event counting is not possible when IOCLK is stopped (in HALT or STOP mode).

Fig. 11-7-4 Event Count Operation

x'0001

IOCLK

TMnBC value

Pin input

(TMnIO)

x'0000 TMnBR value

TMnBR value -1

Count clock

Interrupt request

signal (TMnIRQ)