Bus Controller (BC)

8-49

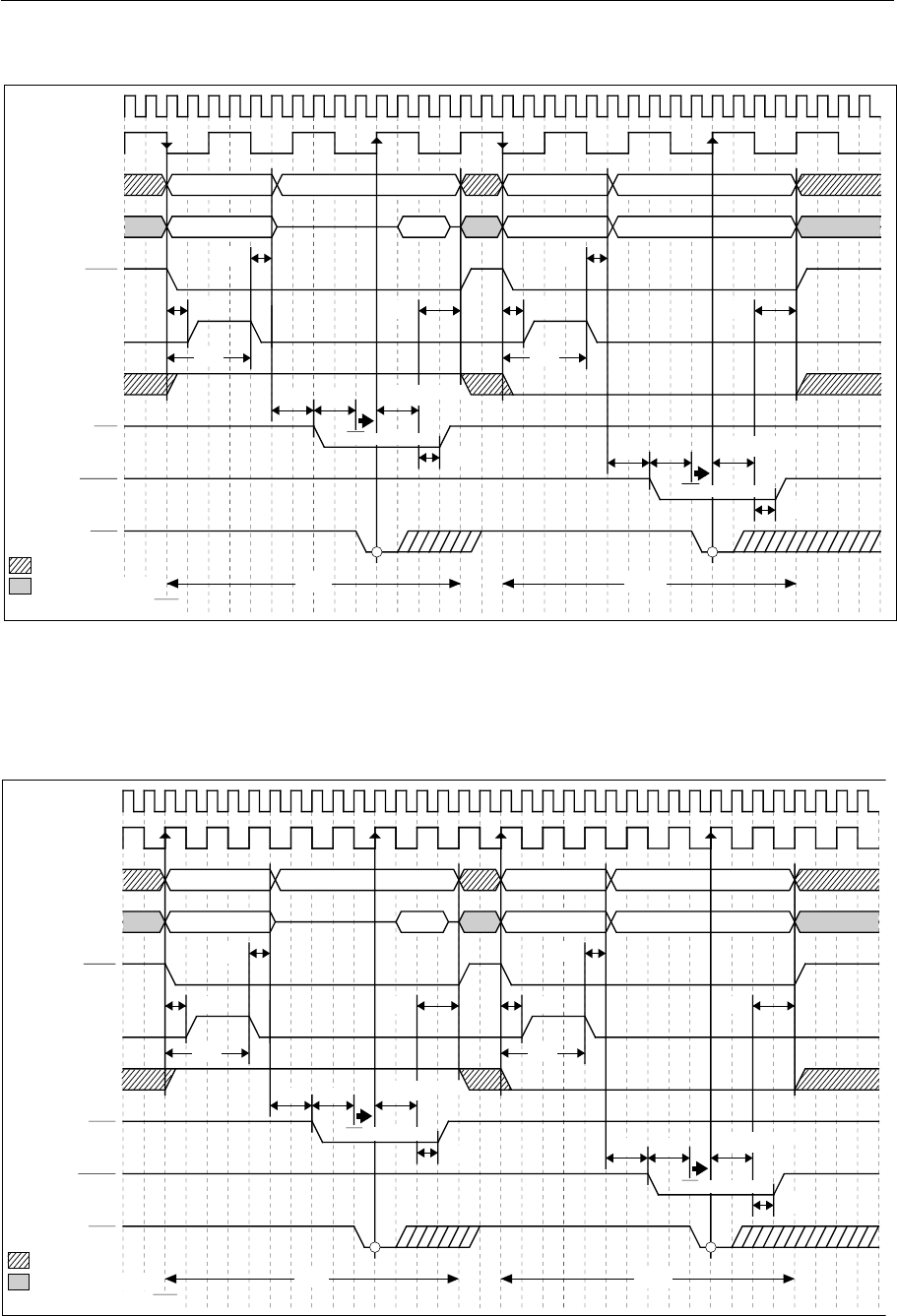

Fig. 8-13-21 Access Timing on a 16-bit Bus with Handshaking, in Synchronous Mode and in

Address/Data Multiplex Mode (MCLK = SYSCLK multiplied by 2)

For details on the various timing settings, refer to the description of the memory control register in section 8.6,

“Description of Registers.”

MCLK

SYSCLK

AS

CSn

ASA

ADE

RWSEL

A23* to 16

ADM15 to 0

RE

WEn

EA

ASN

ASA

ADE

ASN

EA

REN

WriteRead

DK

DW

BCE

WEN

BCE

DW

addr

DK detection start

Consumed internally

by the BC

addr

addr

addr

data in

data out

“0”( )

“L”

: Undefined

*

“0”( )

“L”

Consumed internally

by the BC

DK detection start

: Undefined or Hi-Z

: A23 also serves as CS3

MCLK

SYSCLK

AS

CS2

ASA

ADE

RWSEL

A23* to 16

ADM15 to 0

RE

WEn

EA

ASN

ASA

ADE

ASN

EA

REN

Write

Read

DK

DW

BCE

WEN

BCE

DW

addr

data in

addr

addr

addr

data out

“0”( )

“L”

: Undefined

*

“0”( )“L”

Consumed internally

by the BC

Consumed internally

by the BC

DK detection start

DK detection start

: A23 also serves as CS3

: Undefined or Hi-Z

Fig. 8-13-20 Access Timing on a 16-bit Bus with Handshaking, in Synchronous Mode and in

Address/Data Multiplex Mode (MCLK = SYSCLK multiplied by 4)

For details on the various timing settings, refer to the description of the memory control register in section 8.6,

“Description of Registers.”