Extension Instruction Specifications

3-8

GETCHX (Register high-order 32-bit transfer instruction for multiply-and-accumulate operation: Store)

[Instruction Format (Macro Name)]

GETCHX Dn

[Assembler Mnemonic]

udf12 Dn, Dn

[Operation]

This instruction transfers the contents of the multiply-and-accumulate register MCRH to Dn.

The content of the multiply-and-accumulate overflow detect register MCVF is set in the V flag.

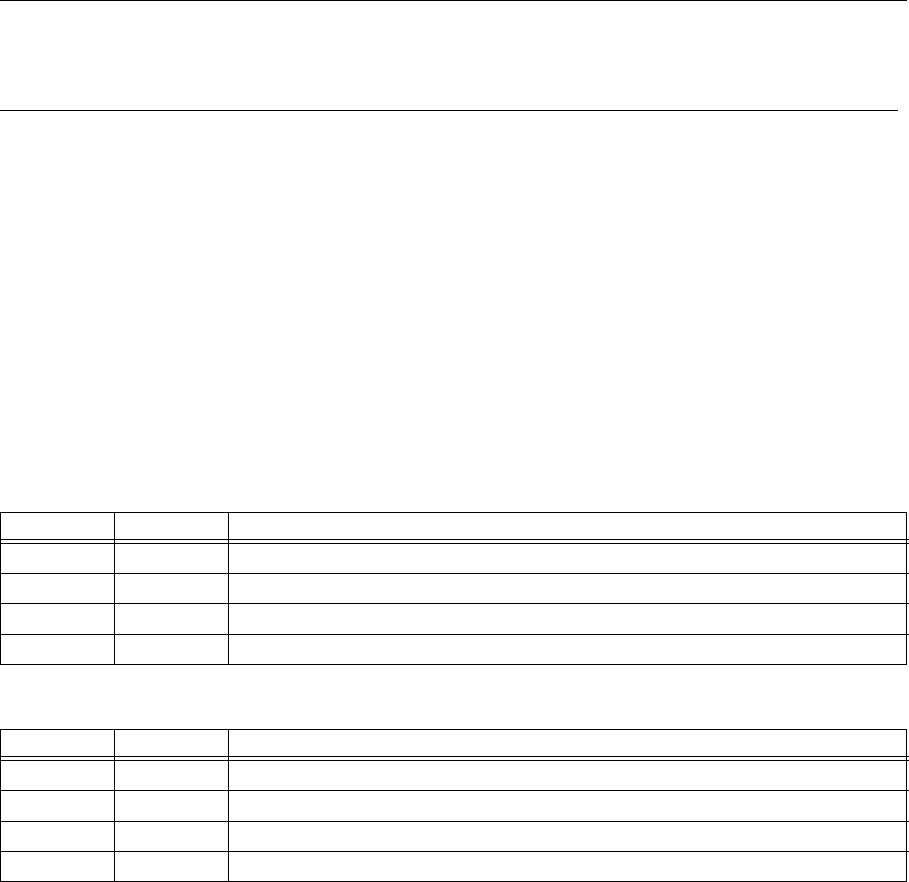

[Flag Changes]

When multiply-and-accumulate operation overflow was not detected (MCVF = 0)

Flag Change Condition

V 0 Indicates that the multiply-and-accumulate operation is valid.

C 0 Always 0

N * Undefined

Z * Undefined

When multiply-and-accumulate operation overflow was detected (MCVF = 1)

Flag Change Condition

V 1 Indicates that the multiply-and-accumulate operation is invalid.

C 0 Always 0

N * Undefined

Z * Undefined

[Programming Cautions]

There is a one-instruction delay in the updating of the PSW to reflect flag changes.

However, the Bcc and Lcc instructions can evaluate the flags without waiting for the flag changes to be reflected in

the PSW.

When "udf12 Dm, Dn" is operated, Dm is ignored.

The operations of "udf12 imm8, Dn", "udf12 imm16, Dn" and "udf12 imm32, Dn" are not assured. In addition, a

system error interrupt does not occur in these cases.