2-14

CPU

2.5 Interrupts

2.5.1 Overview of Interrupts

The most important key to real-time control is the ability to shift quickly to interrupt handler processing.

If an interrupt is generated during the execution of an instruction that requires multiple cycles for execution

(multiplication or division instructions, for example), interrupt response is improved by aborting the execution of

the instruction and immediately accepting the interrupt. After control returns from the interrupt processing program,

the aborted instruction is re-executed.

In addition, by minimizing the resources saved to memory to just the 6 bytes of the PC and the PSW when an

interrupt is generated, the speed of interrupt processing is improved, as is the flexibility of software control.

Furthermore, fast response and optimal program allocation are possible by placing interrupt processing programs at

different addresses for each interrupt level.

This microcontroller has the interrupts shown below. When any of these interrupts occurs, control is shifted to the

appropriate processing program in accordance with the cause.

Reset interrupt

Non-maskable interrupt Priority ranking

Level interrupt n (n = 0 to 6)

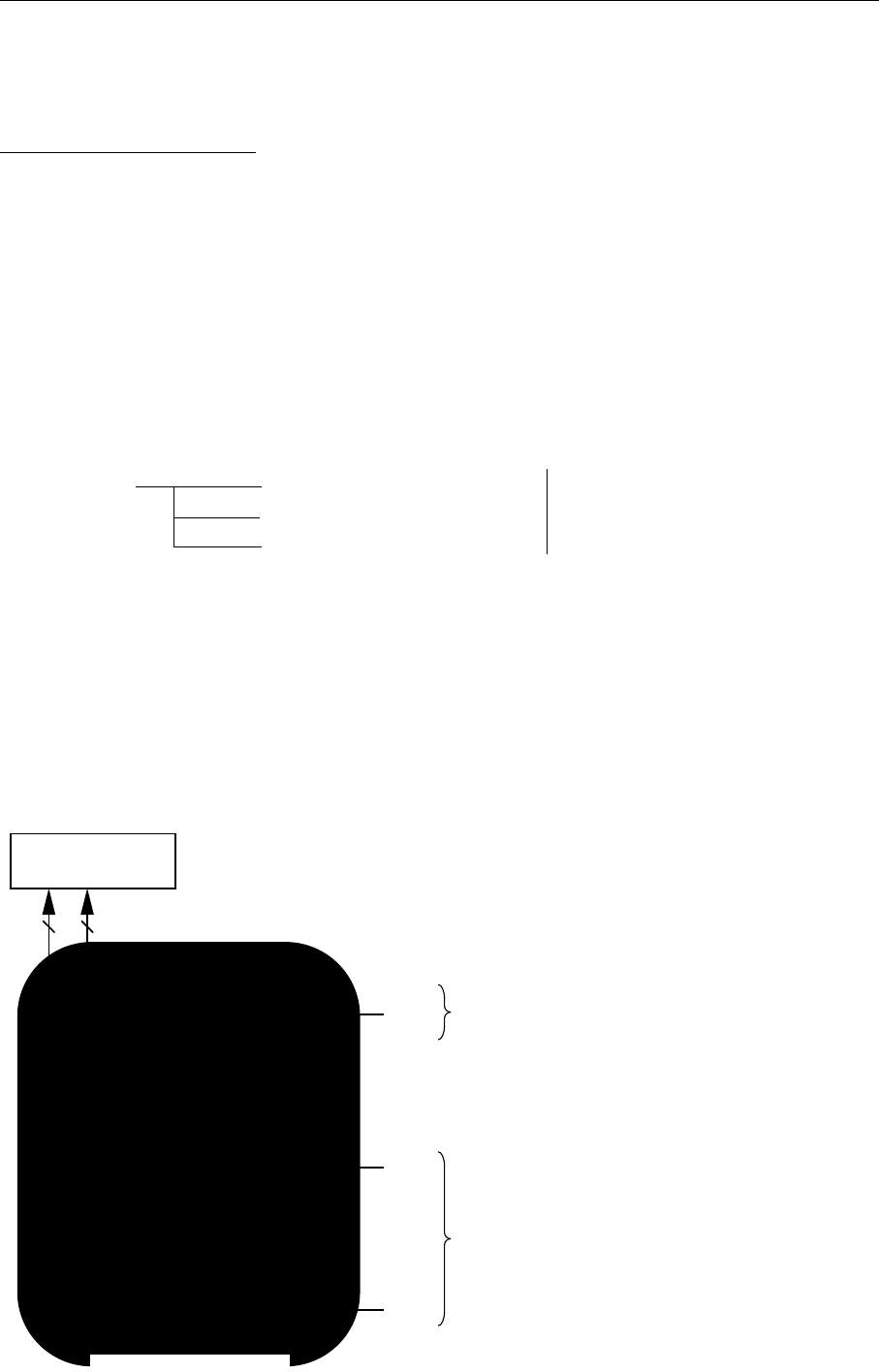

Fig. 2-5-1 shows an overview of the interrupt system. This microcontroller is equipped with 19 interrupt group

control blocks outside the CPU, and controls the interrupts of each group separately. Each interrupt group control

block can accept up to 4 interrupt requests. This allows the controller to support to 38 interrupt factors, providing it

with high expandability and enabling flexible ASIC support.

Except for the reset interrupt, all interrupts from the timer and other peripheral circuits and external pin interrupts

are registered in the interrupt group control blocks. Then, the interrupt requests which pass the interrupt priority

level (level 0 to 6) set in the interrupt group control blocks are output to the CPU. Groups 0 is assigned to non-

maskable interrupts only.

Fig. 2-5-1 Overview of the Interrupt System

➤

Interrupt controller (INTC)

4

Group 0

3 factors are allocated to this group: external pin non-maskable

interrupt, watchdog timer overflow interrupt and system error

interrupt. The remaining factor is reserved.

4

4

Group 2

Group 19

71

Interrupt group control

Interrupt

Interrupt

Interrupt

8 external pin interrupts as well as timer, serial

and other peripheral interrupts are assigned.

Interrupt group control

CPU

Interrupt group control

Non-maskable interrupts

External interrupts