Bus Controller (BC)

8-21

When using handshaking mode (Memory control register 3B B3WM = 1)

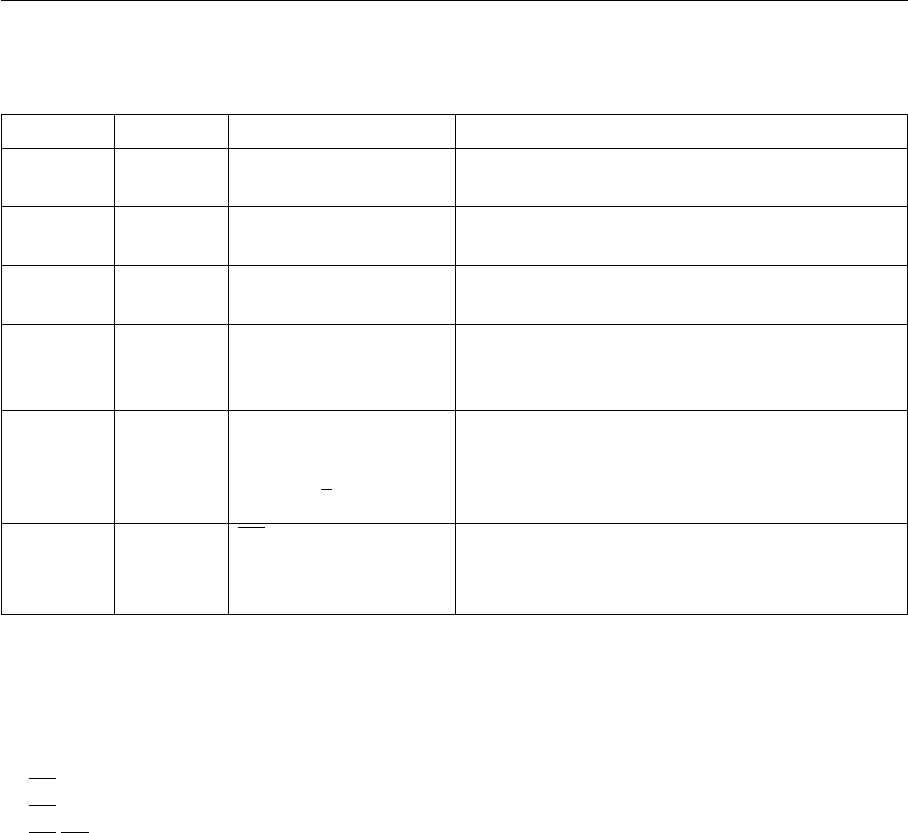

Bit No. Bit name Description Setting conditions

1 WM Block 3 wait mode 1: Handshaking mode

2 BM Block 3 bus mode 0: Synchronous mode (SYSCLK synchronization)

4 BW Block 3 bus width 0: 8 bits

1: 16 bits

7 to 6 ASA1 to 0 AS assert timing 00: 0MCLK

11: 3MCLK

10 to 8 ASN2 to 0 AS negate timing 000: prohibited

Set so that: 001: 1MCLK

ASN ≥ ASA

111: 7MCLK

15 to 11 WEN4 to 0 WE negate timing 00000: 0MCLK

11111: 31MCLK

~

~

~

~

~

~

Note: Handshaking mode can only be set when (MCLK frequency/SYSCLK frequency) = 4.

If (MCLK frequency/SYSCLK frequency) = 1 or 2, set B3WM = 0 in MEMCTR3B.

After the reset is released, block 3 is set as follows:

Address output end timing 3MCLK

RE negate timing 29MCLK

WE negate timing 29MCLK

RE/WE assert timing 3MCLK

Bus cycle start timing 0MCLK

Bus cycle end timing 31MCLK

AS assert timing 1MCLK

AS negate timing 3MCLK

The bus width is 16 bits, and synchronous fixed wait mode is set.